Digital VLSI Design-lecture 5

Timing Analysis

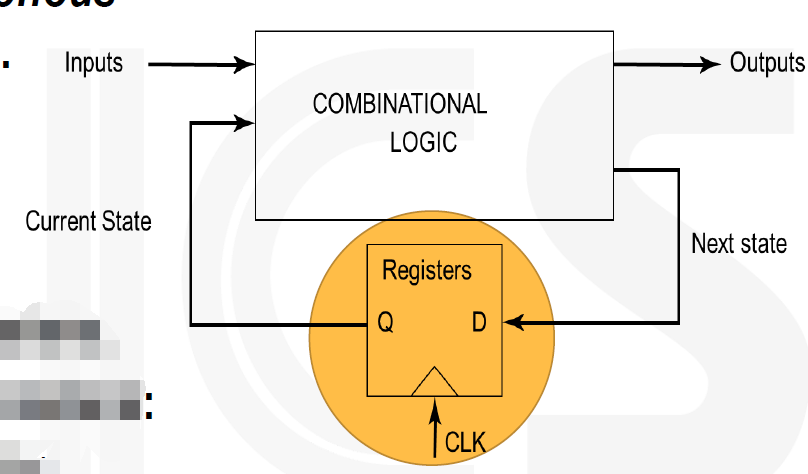

同步设计

大多数数字设计是同步的,并且使用顺序元件构建。

同步设计消除了竞争现象,并且更适合设计流水线,提高了吞吐量。

假设所有顺序元件都是边沿触发的,并使用D触发器作为寄存器。

那么出发它有三个关键的时序参数

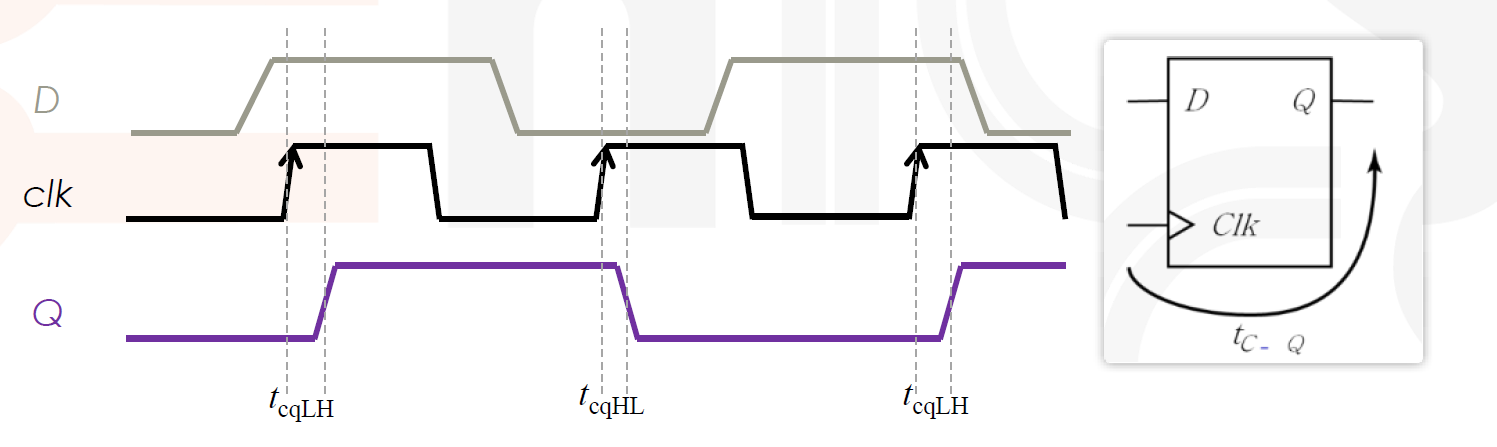

- 时钟到输出延迟,本质上是一个传播延迟。

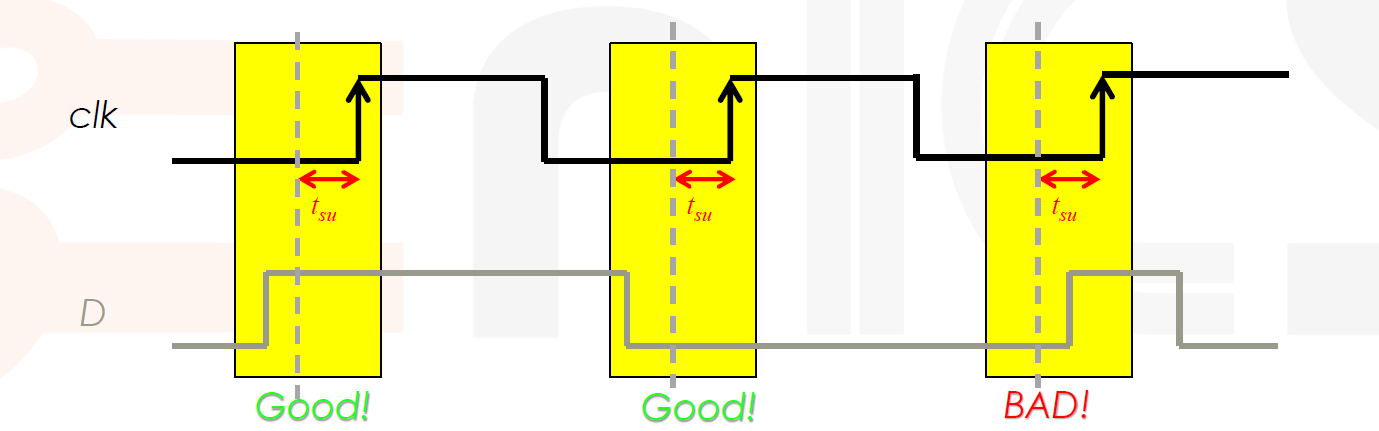

- 建立时间,即数据必须在时钟到来前到达。

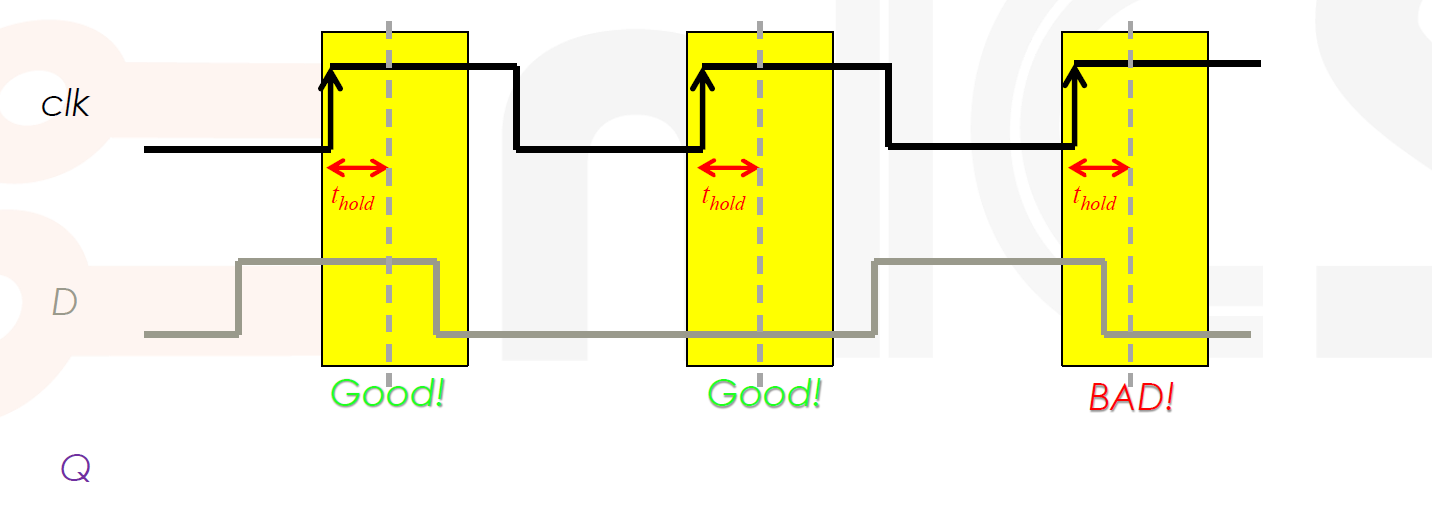

- 保持时间,即数据在时钟到来后必须保持稳定的时间。

时序约束

- 在同步逻辑中,需要思考两个重要参数:

- 最大延迟

- 最小延迟

其最大延迟不能过大,以至于数据信号没有足够的时间从一个寄存器传到下一个寄存器,在下一个时钟沿到来之前还未完成。最小延迟也不能过小,以至于在同一个时钟周期内就穿过了多个寄存器。

最大延迟违例是由于数据路径过长所导致的,包括寄存器的建立时间 ,因此它通常被称为“建立路径(Setup Path)”。

最小延迟违例是由于数据路径过短,导致数据在保持时间 到之前就发生了变化,因此它通常被称为“保持路径(Hold Path)”。

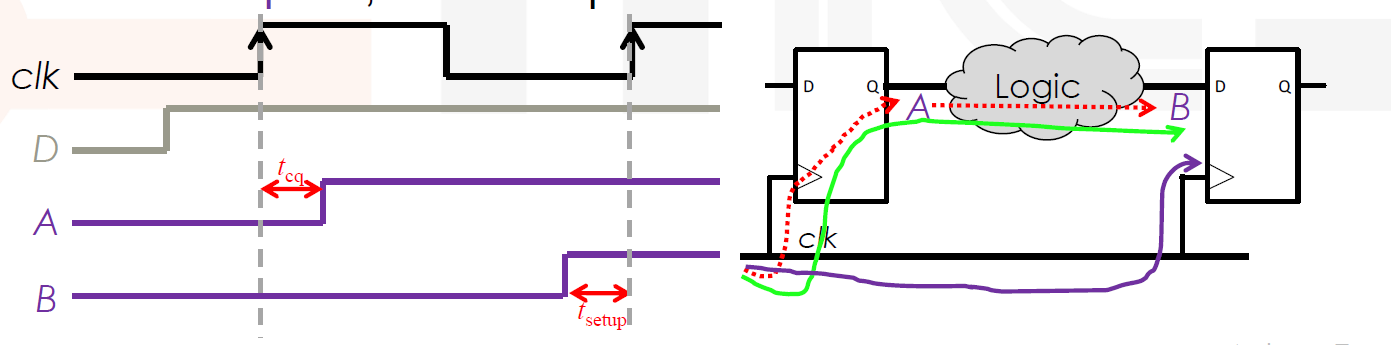

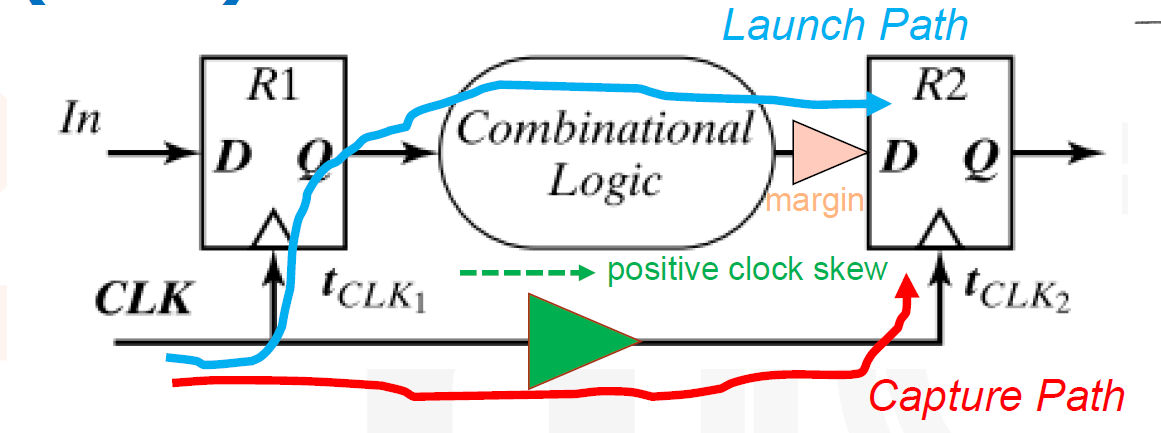

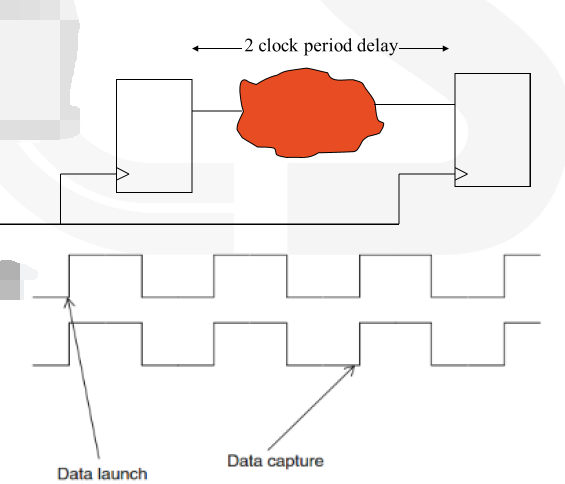

建立最大约束

我们看一看一个时钟周期应该包含哪些内容?

- 时钟上升沿之后,数据传播到 A 有一个延迟

- 接下,必须在下一个时钟周期到来前,提前 到达点 B

我们看图来理解

对于右边图,我们这样看:

- 蓝色路径为启动路径(Launch Path):从第一个寄存器(R1)的时钟沿开始,数据经过组合逻辑。

- 红色路径为采样路径(Capture Path):在第二个寄存器(R2)上采样数据。

- 绿色虚线为正时钟偏移(positive clock skew):R2 的时钟比 R1 晚到。

- 同时,我们还需要留出一点余量(margin)作为安全事件

那么,我们就能建立基本时钟公式

, 为时钟周期。

加入时钟偏移和其他余量之后

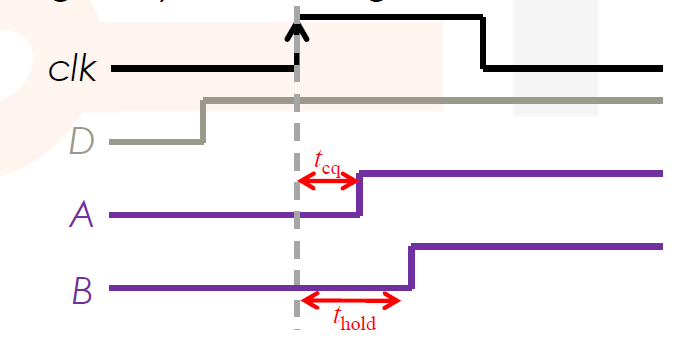

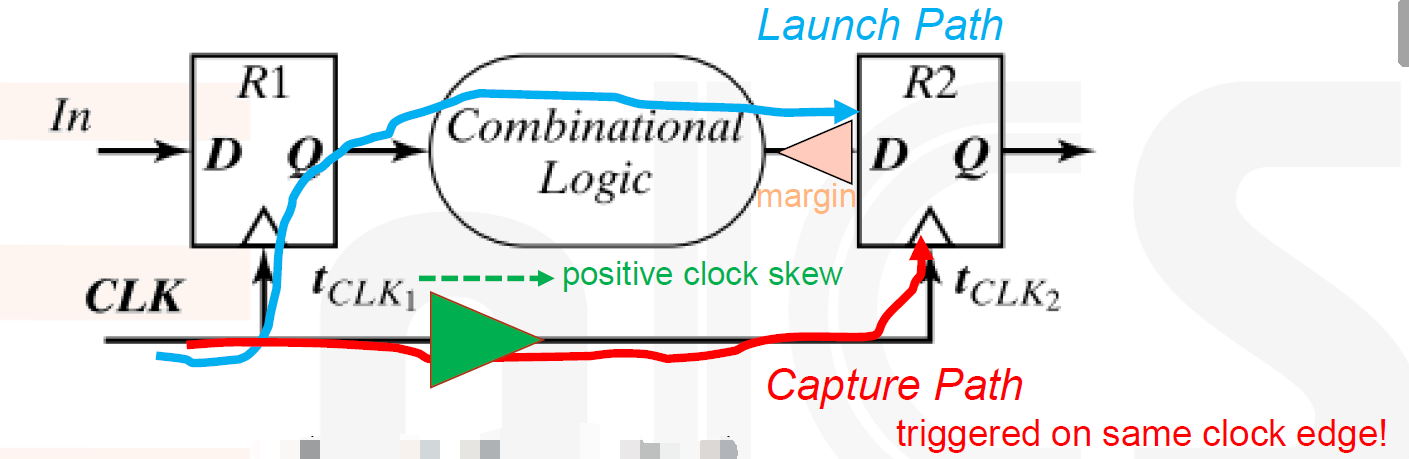

建立最小约束

根据上文,我们显然有

同理,加上偏移和其他余量之后 $t_{cq} + t_{logic} - \delta_{margin}> t_{hold} + \delta_{skew} $

静态时序分析 STA

STA 检查所有可能路径在最坏情况下的传播延迟(最大/最小)。

- 它有以下优点

- 速度比基于时序的门级仿真快很多

- 穷尽式检查 —— 即:每一个(受约束的)时序路径都会被检查!

- 不需要生成输入激励向量(Vector) —— 不需要仿真输入激励。

- 缺点:

- 不检查电路的实际功能是否正确(只关注时序)

- 必须定义时序约束/例外条件

- 同时有许多限制

- 仅适用于同步设计(synchronous design)

- 不能分析组合逻辑反馈环(combinational feedback loops),如用基本逻辑门搭建的触发器

- 不能分析异步时序问题(asynchronous timing),如跨时钟域(clock domain crossing)

- 不会检查异步引脚上的毛刺效应(glitching),如组合逻辑驱动异步置位/复位(set/reset)引脚时的毛刺问题

时序路径

一个时序路径是从起点(Startpoint)到终点(Endpoint)的一条信号传播路径。

- 起点(Startpoint, SP)可以是

- 触发器的时钟引脚

- 输入端口,也称为主输入(Primary Inputs,PI)

- 终点(Endpoint, EP)可以是

- 触发器的数据输入引脚(不包括时钟引脚)

- 输出端口,也称为主输出(Primary Outputs,PO)

- 存储器或硬核宏单元(Hard Macros)

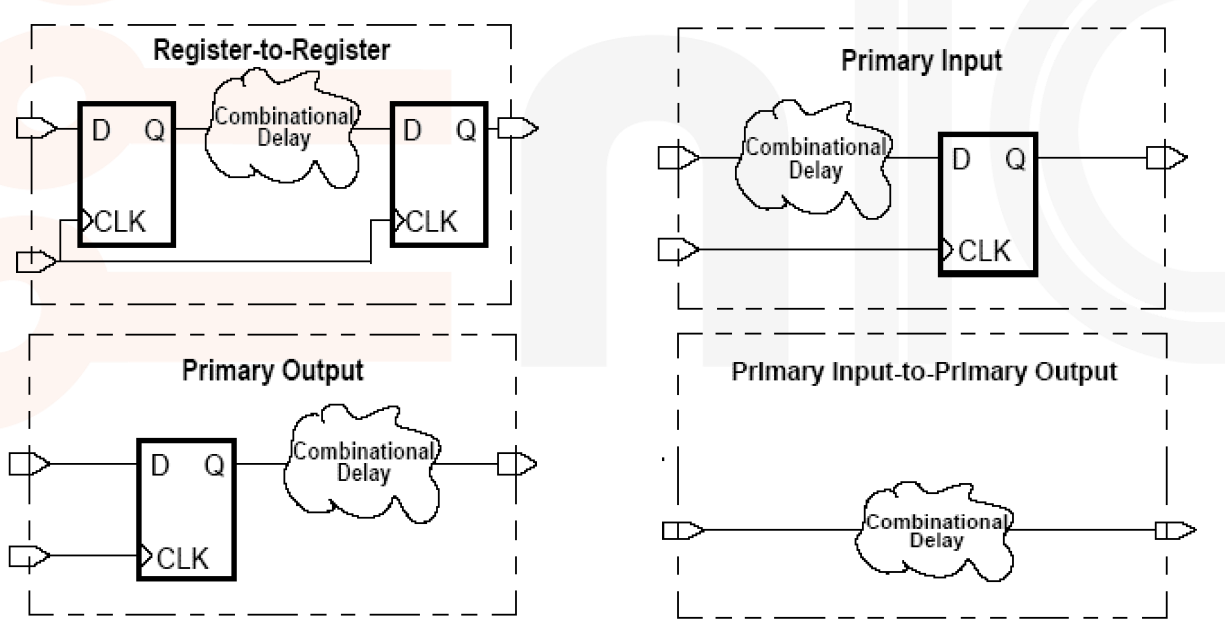

时序路径有以下四种

静态时序分析的目标

- 验证设计中所有路径是否满足最大延迟和最小延迟的约束:

- 从门级网表(Gate-Level Netlist)开始

- 每个逻辑门在标准单元库中都有时序模型(Timing Models)

- STA 工具需要报告所有违反最大/最小延迟约束的路径

- 但这就够了吗?

- 我们只知道了知道所有违反时序约束的路径

- 实际上,还希望知道所有路径的时序信息,并按照路径长短排序

- 并且还需要知道问题出在哪里以去修复

一些基本假设

- 我们的设计是同步的(synchronous),我们只讨论如何处理组合逻辑元件以及最大延迟约束

- 我们假设使用引脚到引脚延迟模型(pin-to-pin delay model),每个门电路从输入到输出有一个固定的延迟值

- 实际上门电路有许多因素影响,例如门类型,负载大小,波形形状,转换方向,具体的引脚位置,随机工艺偏差等

- 实际设计中,这些延迟信息都来自标准单元库的 .lib 文件

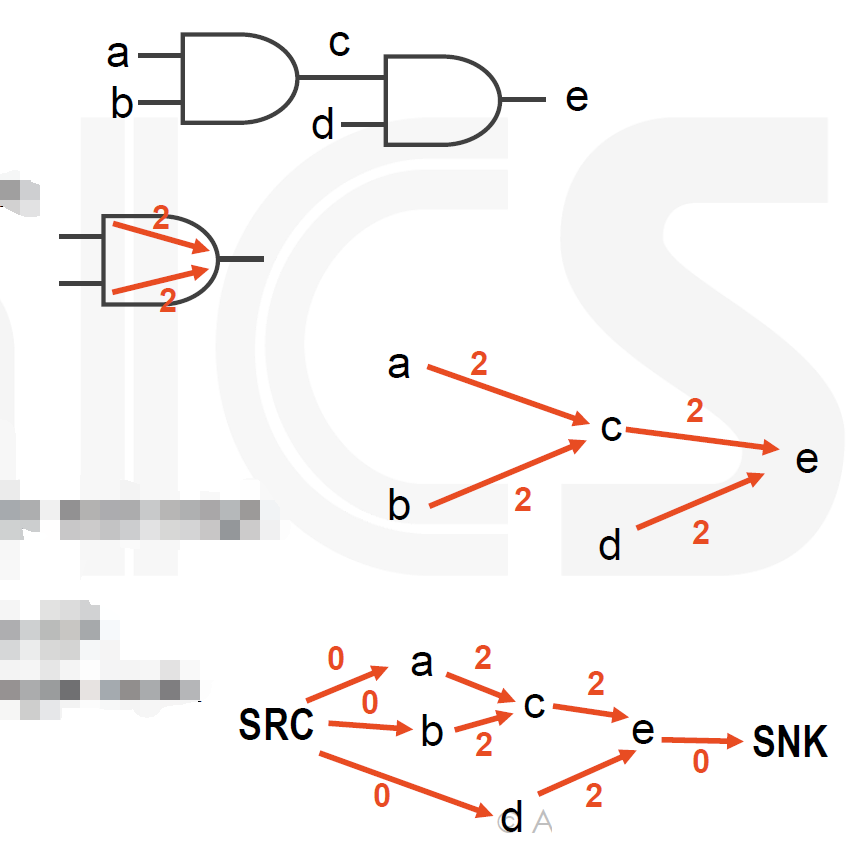

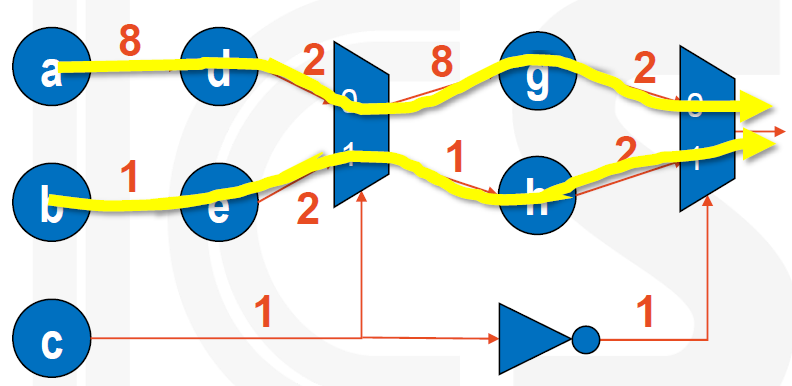

简单路径表示

假设在一个电路中,由两个与门串联,并且每个与门时间延迟是2,我们要将这个电路转化成一个图模型:

- SP 和 EP 转换成顶点,门也转换成一个顶点

- 每个门的输出为一条鞭,每个输入引脚为一条边,并对应延迟信息

- 最后加入源点 SRC 和汇点 SNK ,SRC 连接所有 SP, 所有 EP 连接 SNK

- 如果我们去穷举所有路径,路径数量会呈指数级增长,计算量巨大。因此,我们使用基于节点的分析方法,它:

- 对于每一个节点,只找出所有路径最长延迟

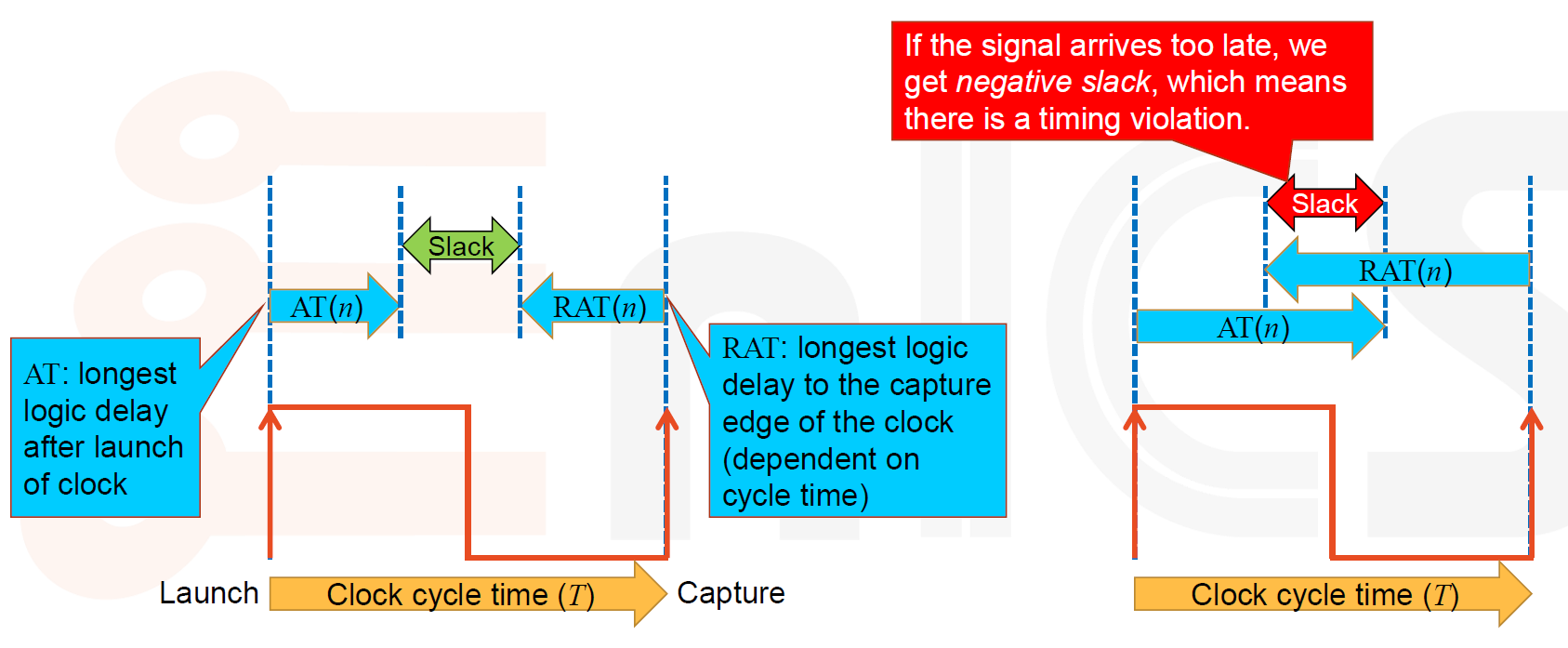

- 定义节点的到达时间(Arrival Time, AT)为从源点(SRC)到当前节点的最长路径时间

- 定义节点的要求到达时间(Required Arrival Time, RAT)为信号最晚允许从该节点出发的时间

节点的 Slack 定义为:

对于计算 AT 和 RAT 由于这是个 DAG ,我们直接使用拓扑排序 + DP 即可。

这幅图可以更生动说明 Slack 的含义。

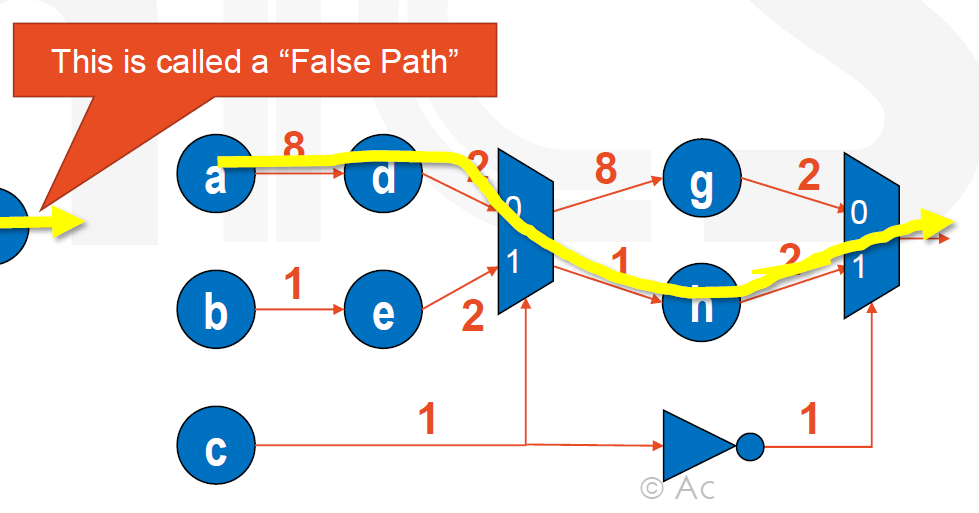

假路径

我们计算的时候,已经假定图一定是联通的,但是结合上电路逻辑的话,就不一定联通,一些路径在拓扑上存在,但也永远不会激活,这种路径被称为假路径。

设计限制

时序约束

STA 工具怎么知道我们想要的时钟周期是多少呢?

- 它不知道,我们得告诉它,我们必须为设计定义约束

- 这通常是通过 SDC 语法(Synopsys Design Constraints) 来完成的,这是一种基于 Tcl 的扩展语法

有三种主要的时序约束:时钟定义、建模芯片外环境、时序例外情况。

集合

即使你会使用 TCL , EDA 工具还或使用另外一种的数据结构,称为 “集合” 。

集合和 TCL 列表类似,但是它的值是指针,必须使用专门函数 foreach_in_collection 遍历集合

这里不展开。

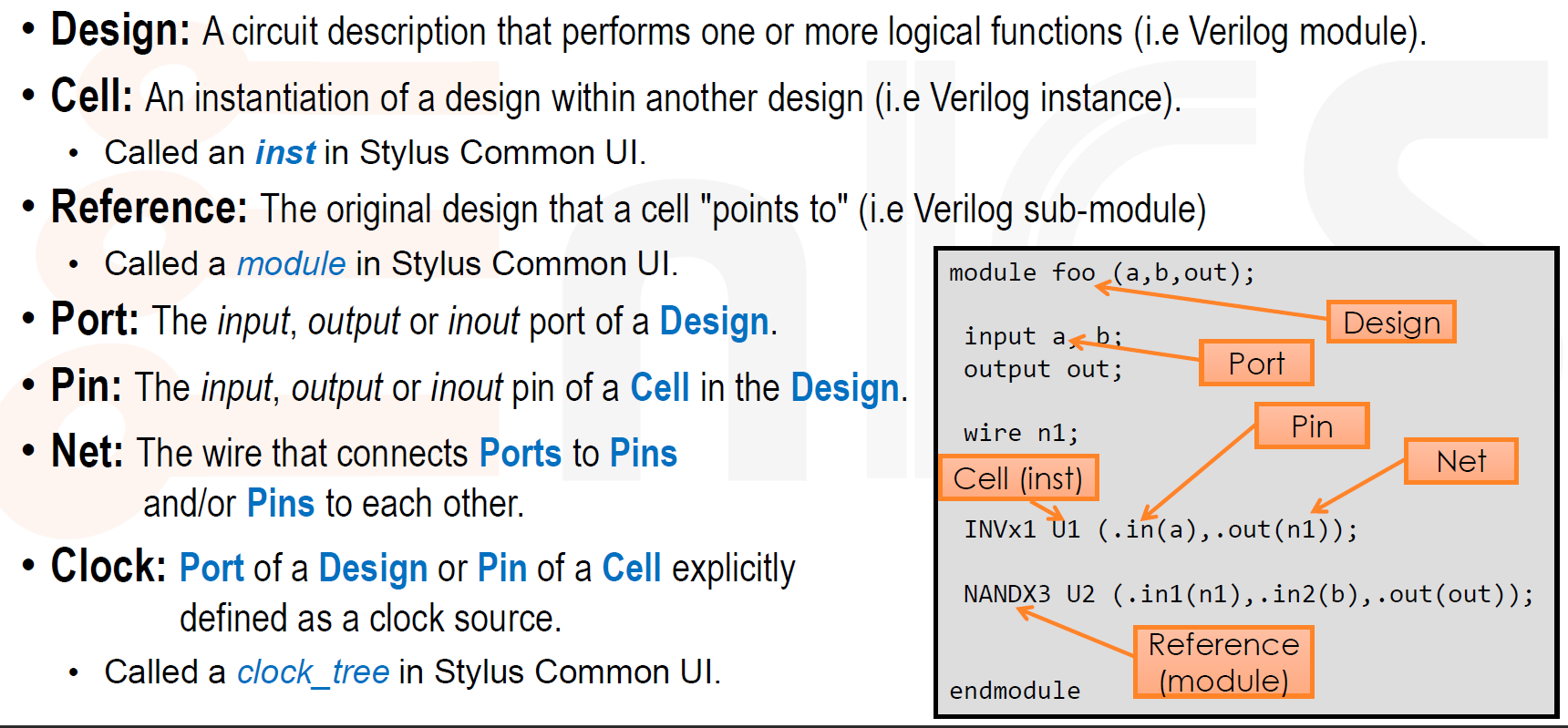

设计对象

这几个术语都比较简单,直接用 ppt 内容

几个有用的函数

这些函数都返回集合,而不是 TCL list

-

get

-

[get_ports string]返回所有匹配该字符串的 端口(ports) -

[get_pins string]返回所有匹配的 引脚(pins)(包括 cell/macro 内部的) -

[get_nets string]返回所有匹配的 线网(nets) -

all

-

[all_inputs]返回该模块的所有主输入端口(primary inputs) -

[all_outputs]返回该模块的所有主输出端口(primary outputs) -

[all_registers]返回该模块中的所有寄存器(通常是 D 触发器)

时钟定义

- 为了设置 SDC 时序约束,我们必须定义一个时钟,这需要注意:

- 时钟来自哪里?(例如:输入端口、PLL 输出等)

- 时钟周期是多少?

- 时钟的占空比是多少?

通过 create_clock -period 20 -name my_clock [get_ports clk] 定义一个时钟。

我们可以定义多个时钟,但必须注意时钟域交叉。

在综合中,我们可以用这个命令假设时钟是理想的,STA 工具不会考虑时钟路径上的延迟

set_ideal_network [get_ports clk]

但为了更贴近真实的时序,我们应该给时钟添加上升/下降时间(ns):

set_clock_transition 0.2 [get_clocks my_clock]

我们还可以加入时钟抖动(ns)

set_clock_uncertainty 0.2 [get_clocks my_clock]

最后,在完成时钟树综合(CTS)后,我们不再认为时钟是理想的,STA 工具会考虑实际时钟路径上的延迟和缓冲器,进行更精确的时序分析。

set_propagated_clock [get_clocks my_clock]

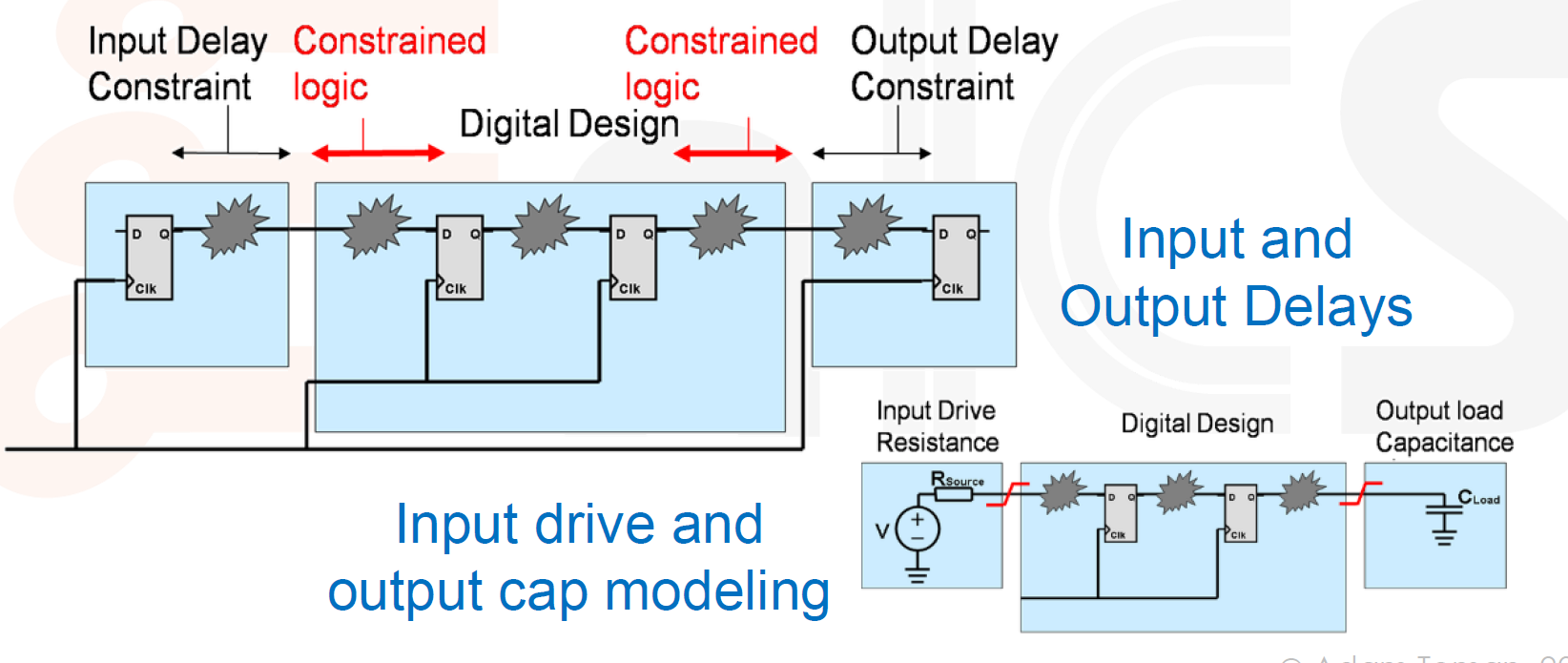

I/O 限制

现在时钟已经定义完成,reg2reg 的路径也同时被限制,但是 in2reg, reg2out,in2out 的路径怎么办呢?

- 这需要思考以下两个问题

- 哪个时钟在驱动 I/O 端口?

- 芯片外部延迟又该如何建模?

通过时钟设置 IO 延迟

1 | set_input_delay 0.8 -clock clk \ |

这表明外部输入数据会在时钟边沿前 0.8ns 到达,内部数据必须在时钟边沿后 2.5ns 内传到输出端口,且排除时钟本身不作为输入信号处理。

更好的方法是使用虚拟时钟来定义环境模型,但是这里不介绍。

物理方法定义

此外还有一种方式是定义最大 I/O 延迟

1 | set_max_delay 5 \ |

此外,我们还必须为输入信号设置驱动特性

1 | set_driving_cell -cell [get_lib_cells MYLIB/INV4] -pin Z \ |

最后,还需要为输出信号设置负载电容(Load Capacitance)

1 | set_load $CIN_OF_INV [all_outputs] |

$CIN_OF_INV 是一个定义好的负载值(例如 INV 门的输入电容),这种方式常用于门级网表后 STA 分析或没有完整 I/O 模型时。

我们可以用一张图总结目前学到的 io 延迟:

时序例外情况

某些路径不需要被正常分析和优化,这就叫时序例外(Timing Exceptions)

路径不会同时起作用

如图所示这两条黄色路径不会同时起作用,因此我们要让 STA 避免考虑这两条路径的相互影响,这在 tcl 语言是这样定义的:

1 | set_false_path -through [get_pins mux1/I0] -through [get_pins mux2/I0] |

这些命令表示:STA 不需要检查这些通过特定输入的路径

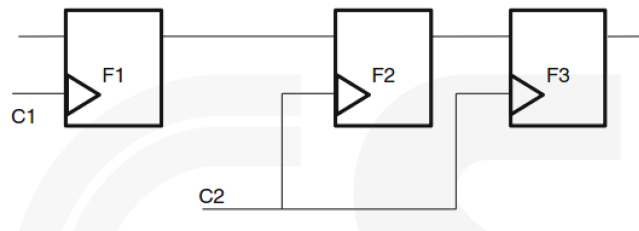

跨时钟域的数据传输

数据从时钟 C1 域的寄存器 F1 传输到时钟 C2 域的寄存器 F2

1 | set_false_path -from F1/CP -to F2/D |

或者使用时钟组工具,告诉 STA 这两个时钟互质

1 | set_clock_groups -logically_exclusive \ |

如果是“等相位”的慢时钟到快时钟的传输,如图所示:

我们可以设置多周期路径:

1 | set_multicycle_path -setup -from F1/CP -to F2/D 2 |

状态分析

在很多设计中,会有一些信号始终为某个常数值,例如设置某个寄存器以进入某种工作模式,在这种情况下,许多路径都是假路径:

- 如果常数信号接在 MUX 选择线上,那么某些路径永远不会被选中

- 如果某个 AND 门输入是 0,那么输出始终为 0,另一路输入变化也没意义

所以我们希望把这个常数传播到整个电路中,从而让 STA 工具忽略这些不相关的路径.

1 | set_case_analysis 0 [get_ports TEST_MODE] |

设计违例规则

最大转换时间,最大电容负载,最大扇出数等。

1 | set_max_transition $MAX_TRAN_IN_NS |

面向良率的高级静态时序分析

高级STA内容会在课程后期讲解,你将会学习一些常见的概念和术语:

- On-Chip Variation (OCV)

- Advanced On-Chip Variation (AOCV)

- Signal Integrity (SI)

- More and more and more

时序检查

之前已经知道最大延迟和最小延迟了,但是在实际中,我们还需要考虑以下内容:

- 恢复(Recovery)

- 移除(Removal)

- 时钟门控(Clock Gating)

- 最小脉宽(Min Pulse Width)

- 数据到数据(Data-to-Data)

Recovery, Removal and MPW

恢复检查:异步控制输入端在去使能(deasserted)之后,到下一个时钟沿(有效沿)到来之前,必须保持稳定的最短时间。

移除检查:异步控制输入端在去使能(deasserted)之前,从上一个时钟沿(有效沿)之后开始,必须保持稳定的最短时间。

最小时钟脉宽(MPW):从一个时钟上升沿或下降沿开始,时钟信号必须保持稳定的最短时间。

时钟门控检查

时钟门控是指在时钟路径上出现阻止时钟传播的信号,时钟门控的使能路径必须比时钟信号提前足够的时间到达,以确保无毛刺的功能(同时在时钟沿之后也要保持一段时间)。

命令

report_analysis_coverage 检查你是否已经完全约束了你的设计。

check_timing 执行一系列时序约束的一致性与完整性检查,以确保设计中指定的约束是合理且完整的。

或许在任何综合或布局布线工具中,最重要的命令是 report_timing。

这一部分请通过 ppt 学习

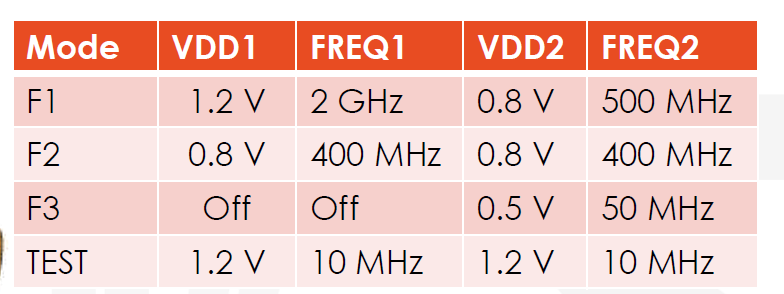

Multi Mode Multi Corner

在综合期间,我们(通常)针对最坏情况进行时序目标设定,但是最坏情况是什么?

直观来看,那就是慢速角落(例如 SS 工艺,VDD -10%,125°C)

不需要进行保持时间(hold)检查,因为时钟是理想的。

但是还有其他工作模式怎么办?例如测试模式,我们是否需要在相同(高)时钟速度下完成时序收敛?

为了解决这个问题,只需要准备一个额外的 SDC 文件并重新运行 STA / 优化。

1 | # 设置工作模式为测试模式 |

但在真实设计中,情况只会更多,有多个工作模式和电压域,使用真实时钟时,还需要注意保持时间,很容易面对上百种 corner。

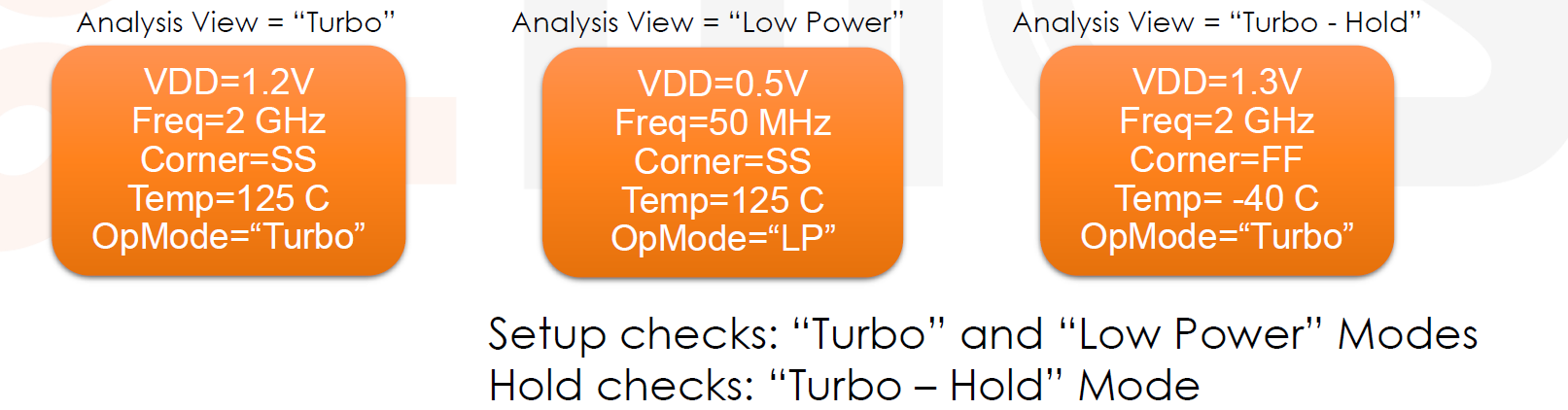

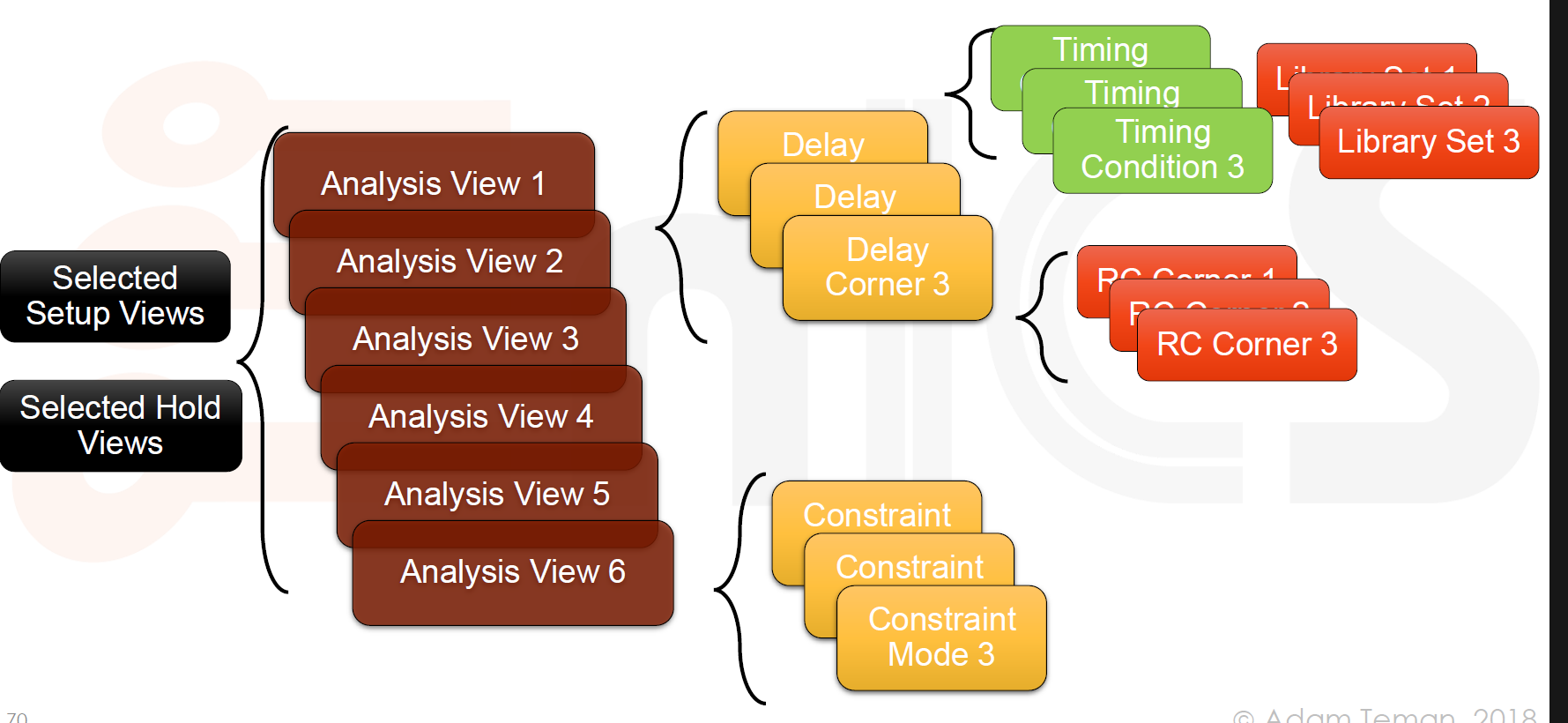

分析视图

为了简化设置,我们创立分析视图,为 setup 和 hold(即最大和最小)时序约束选择使用哪一个视图。

一个分析视图是由一个延迟工况和约束模式构成的。

1 | create_analysis_view -name turbo \ |

延迟工况告诉工具该如何计算延迟,所以它包含了时序库和寄生参数提取规则。

约束模式本质上是对应某个特定工作模式下的 SDC 约束命令和条件集合。

约束模式

一个约束模式就是一组相关的 SDC 文件,当你在多个分析视图之间切换时,STA 工具会自动将相关约束应用到设计中

1 | create_constraint_mode -name turbo_mode -sdc_files {turbo.sdc} |

延迟工况

而延迟工况则要复杂一些,它由一个时序条件、一个 RC 工况以及其他一些我们现在不讨论的内容组成。

1 | create_delay_corner -name slow_corner_vdd12 \ |

时序条件和库集合

别急,我们还没完,一个时序条件是一组库集合,用于某个特定的电源域,我们要将时序条件和库集合关联起来。

1 | create_timing_condition -name tc_ss_1p2V_125C \ |

一个 库集合(library set) 是一些 .lib 表征文件的集合,这些文件会被用来对相关门电路进行时序建模。

这包括标准单元和其他宏单元,如 RAM 和 I/O。

有时还会包含用于噪声分析的 “SI” 表征数据。

1 | create_library_set -name ss_1p2V_125C \ |

RC 工况

RC 工况是一组用于 RC 提取的规则集合,它可能包含一个用于快速提取的“电容表”,以及一个用于精确提取的 QRC 技术文件(techfile)。

1 | create_rc_corner -name RCmax -cap_table ${tech}/RCmax.CapTbl -T {125} \ |

(完)