Digital VLSI Design-lecture 6

Lecture 6: Moving to the Physical Domain

我们已经完成了设计流程的前端部分,现在开始完成后端部分

- 我们将通过绘制布局图(floorplan),为我们的设计打下物理基础。

- 这包括决定“重要”或“较大”的模块放置位置,比如 IP 核、I/O、供电网格、特殊布线等。

- 接下来,我们可以放置(place)逻辑门,同时考虑拥塞(congestion)和时序(timing)因素。

- 有了触发器之后,我们就可以设计时钟树(clock-tree)。

- 最后,我们可以根据设计规则检查(DRC)、时序(timing)、噪声(noise)等因素,对所有网络进行布线(route)。

- 在流片(tapeout)之前,我们还需要清理设计、验证等等。

开始物理设计

为了从理论设计走向物理芯片,我们先在理论上定义了:

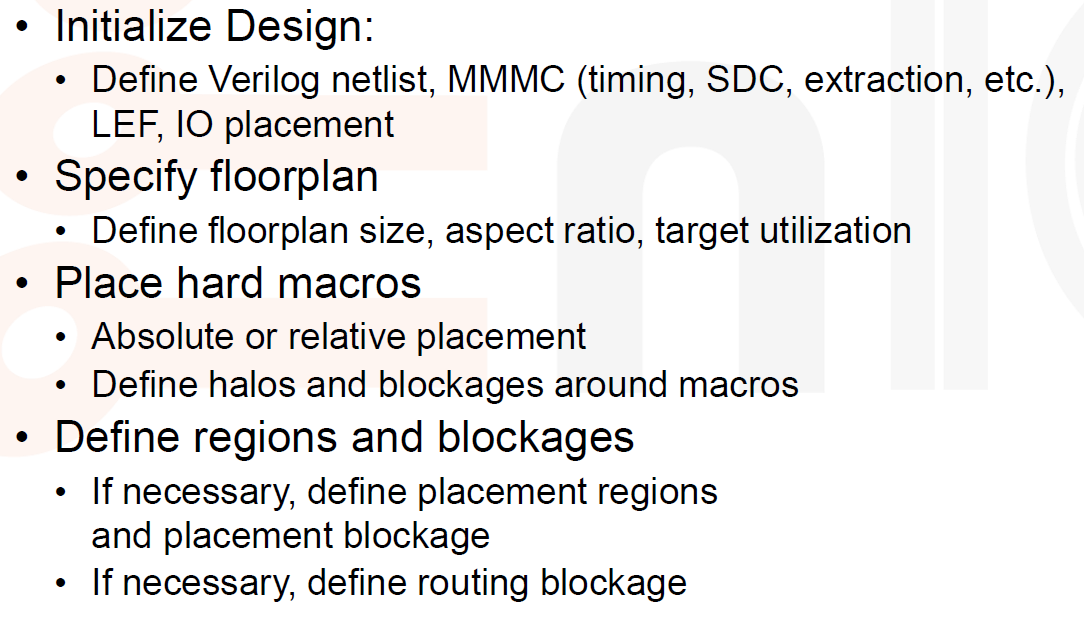

- 定义设计

.v - 定义设计约束/目标

.sdc - 定义工作条件/模式 (MMMC)

- 定义工艺和库信息

.lef - 定义物理信息(Floorplan)

在之前的理论设计中,我们用的是一个理想的模型,因此忽略了以下内容:

- 不考虑电源供电

- 综合时只认为有一个完美的VDD在供电,实际上电源会有压降、电流密度限制等问题。

- 不考虑实体物理连接

- 综合时只用“连接线”表示信号连接,而不考虑实际物理距离、电阻、电容、金属层等。

- 不考虑时钟网络非理想性

- 综合默认时钟是理想的、瞬时到达的,实际上时钟会有延迟、不平衡(skew)、抖动等问题。

我们必须补全这些被忽略的问题:

- 定义全局网络

- 比如告诉工具:哪些网是电源(VDD)、地(GND)、时钟(CLK),并与每个 cell 实例建立连接。

- 提供工艺规则和单元信息

- LEF 文件描述单元的物理尺寸、金属层使用情况、布线约束等,是物理工具理解电路布局的基础。

- 提供物理单元(逻辑上非必须)

- Tie cells , P/G pads , DeCaps , Filler cells , etc.

- 定义 Hold 时间约束和操作条件(MMMC)

- 设置低功耗定义,例如电压域(voltage domains)、电源开关(power gates)、基体连接(body taps)等。

Multiple Voltage Domains(MVD)

多电压域设计

- 首先必须定义电压域:

- 创建电源域名称

- 列出连接到不同电源的单元(例如:VDD1、VDD2、GND1 等)

- 绘制每个电源域的区域边界

- 放置宏单元

- 考虑以下内容:

- 布线拥塞

- 朝向

- 通常手动放置效果比自动放置更好

- 考虑以下内容:

- 放置电源开关

- 为可关断的电源域(power down domains)放置开关

电平转换器

如果模块工作在不同电压下,当它们之间通信时,电平不一致会造成信号传输错误或器件损坏。因此必须使用电平转换器。

电源门控

本科生没必要掌握这个,这个坑后面填

Floorplanning

Floorplanning 是一种映射关系,它在逻辑描述(如 netlist,网表)与物理描述(如 floorplan,布局图)之间建立联系。

布局规划的目标(Goals of floorplanning)

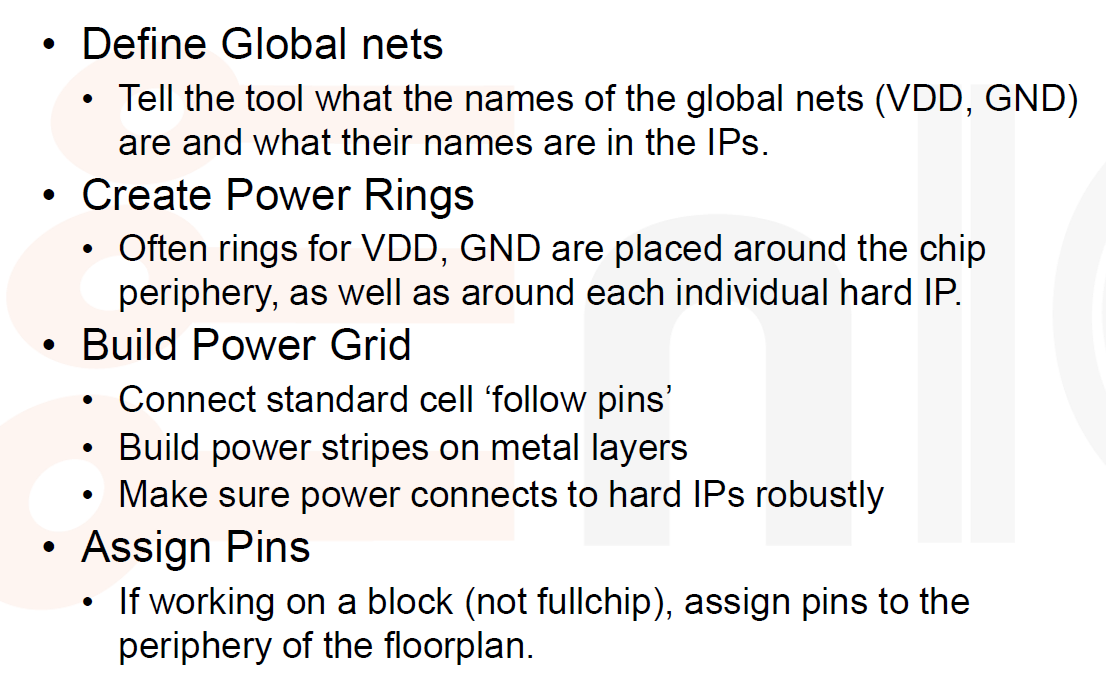

- 安排芯片上的各个功能块(blocks)的位置

- 决定 I/O 引脚(I/O pads)的位置

- 决定电源引脚(power pads)的数量和位置

- 决定电源分布(power distribution)的方式

- 决定时钟分布(clock distribution)的方式与位置

布局规划的具体任务(Objectives of floorplanning):

- 最小化芯片面积(chip area)

- 最小化时延(delay)

- 最小化布线拥塞(routing congestion)

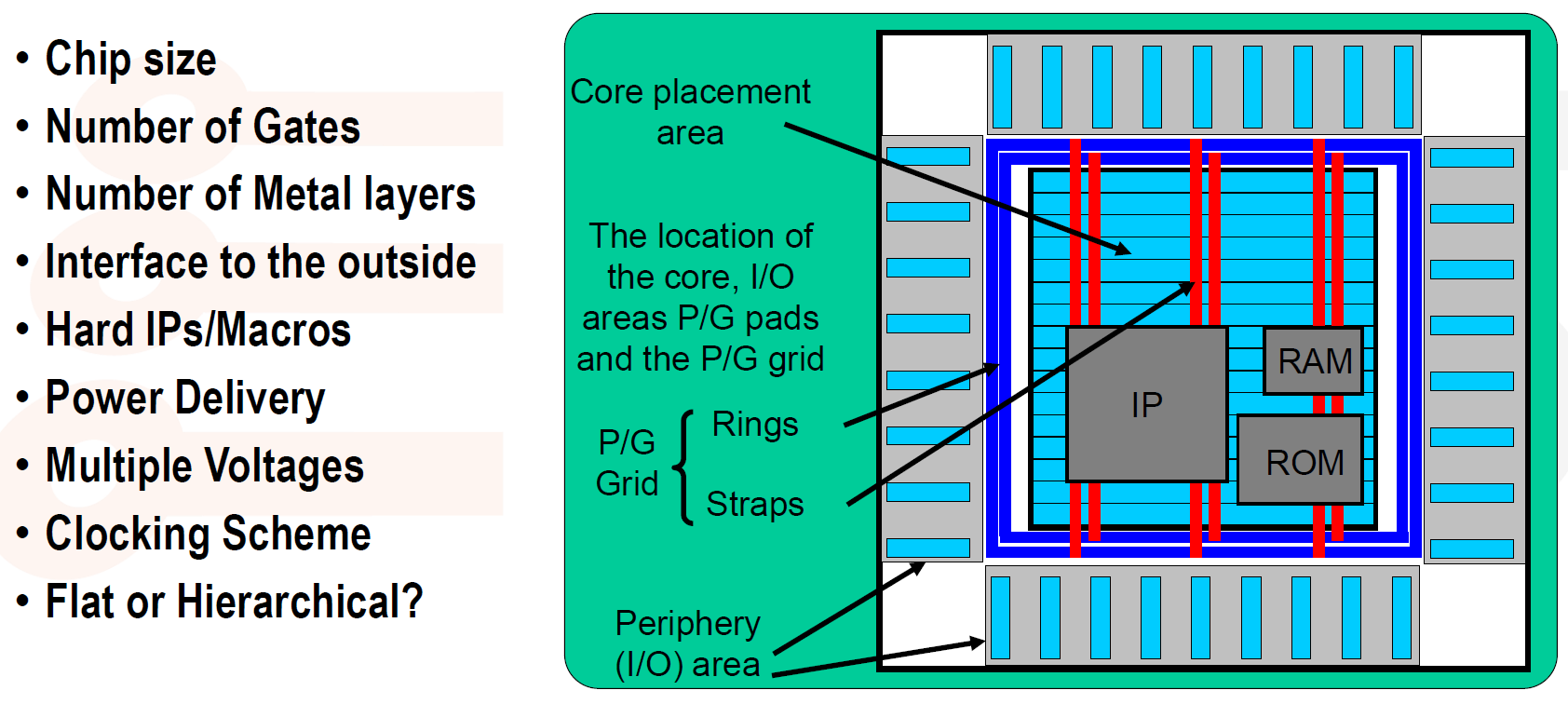

在整个芯片 Floorplan 时,还需要考虑以下因素:

- 芯片尺寸(Chip size)

- 门数量(Number of Gates)

- 金属层数(Number of Metal layers)

- 对外接口(Interface to the outside)

- 硬核 IP 或宏单元(Hard IPs/Macros)

- 电源供给方式(Power Delivery)

- 多电压供电(Multiple Voltages)

- 时钟方案(Clocking Scheme)

- 设计结构是扁平还是层次化(Flat or Hierarchical?)

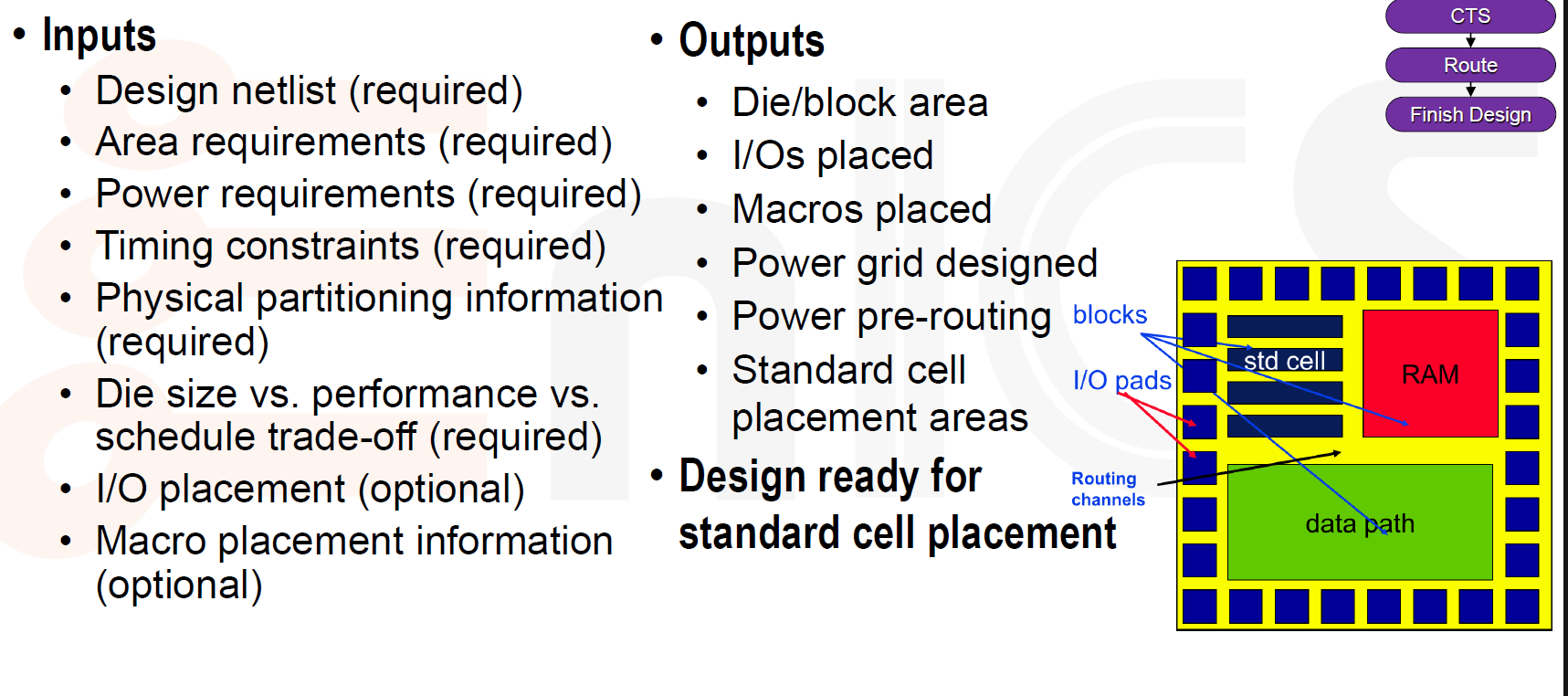

输入和输出

IO环

引脚配置(pinout)通常由前端设计人员决定,并会征求物理设计工程师和封装工程师的意见。

I/O 引脚并不会像摩尔定律那样随工艺缩小而变小,所以从面积角度来看,它们是非常昂贵的资源。

I/O 引脚不仅用于将信号连接到外部世界,它们还负责为芯片供电。

因此,I/O 规划是芯片布局规划中至关重要的核心环节。

但是稍后我们再继续这个话题

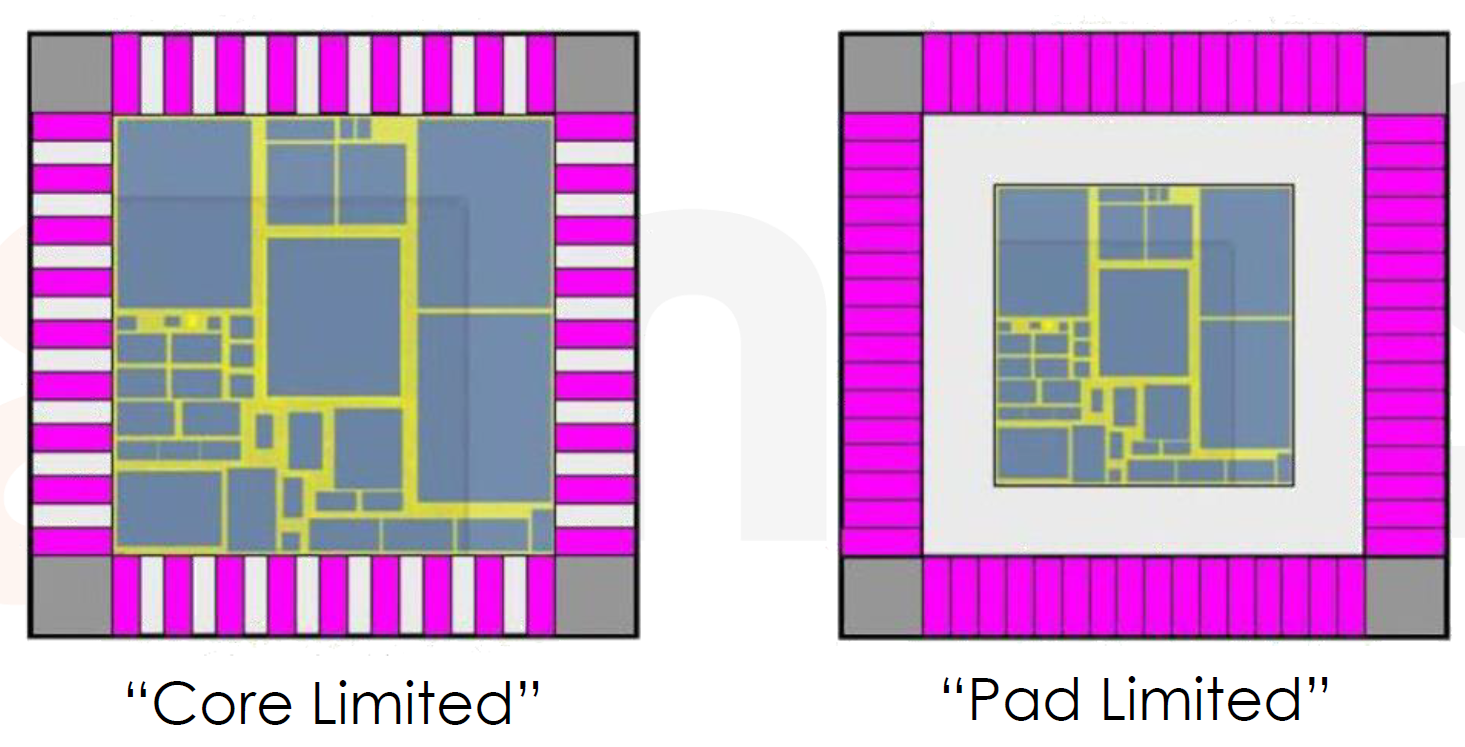

选择合适的芯片尺寸

芯片尺寸由核心面积和引脚数量同时限制,这张图能讲得更加明白

利用率

Utilization 指的是核心区域中被标准单元(standard cells)占据的面积比例。一个常见的起始利用率为 70% ,实际情况中随着设计原因,利用率会更高和更低。

-

高利用率会带来以下问题:

- 布线拥塞

- 对优化和合法化阶段产生负面影响

-

局部拥塞

- 某些单元,如多路复用器(multiplexers)引脚密集,即使整体利用率合理,局部仍可能拥堵

- 像多路复用器这类引脚密集的单元可能造成局部拥塞,所以仅凭利用率并不能完全决定芯片尺寸。

- 建议先进行一次试布线以检查布线拥塞情况

- 可以通过优化综合或增加布线资源来改进

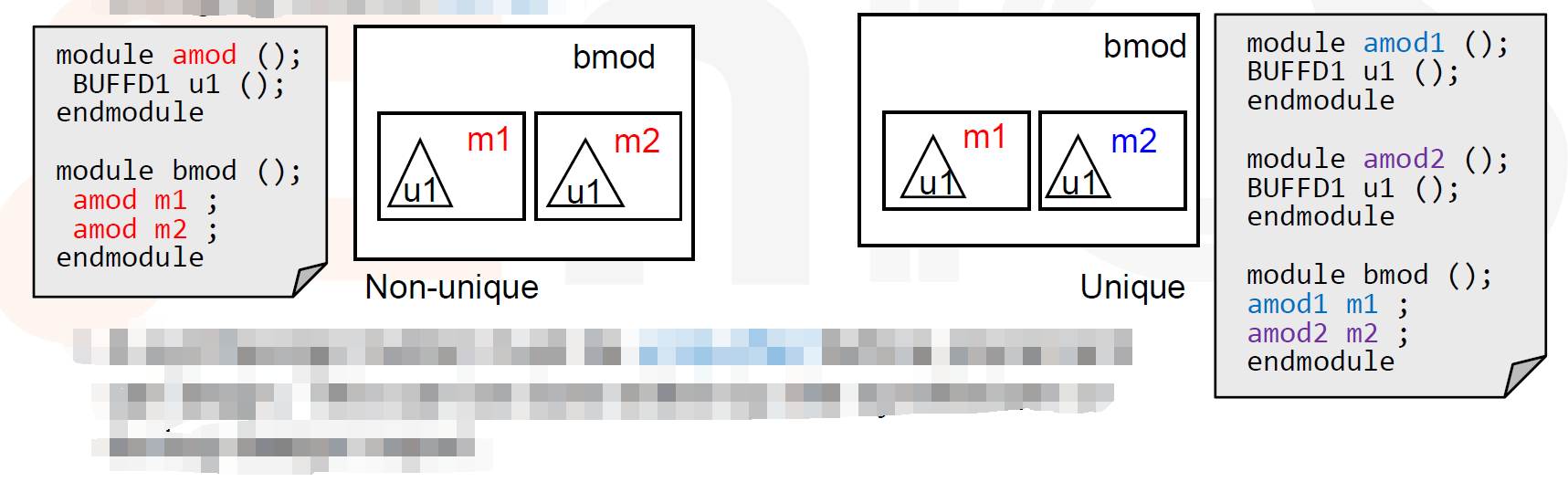

唯一化网表

当进入物理当进入物理设计阶段时,网表必须是唯一的,一个唯一的网表意味着每个子模块只被引用一次。

综合生成的网表必须在布局前进行唯一化,可以由综合器完成,也可以在设计导入阶段完成。

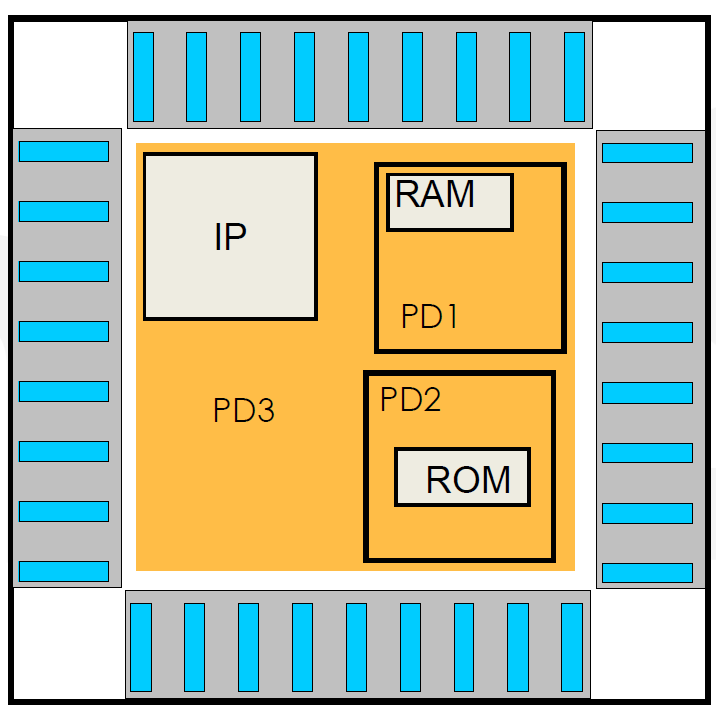

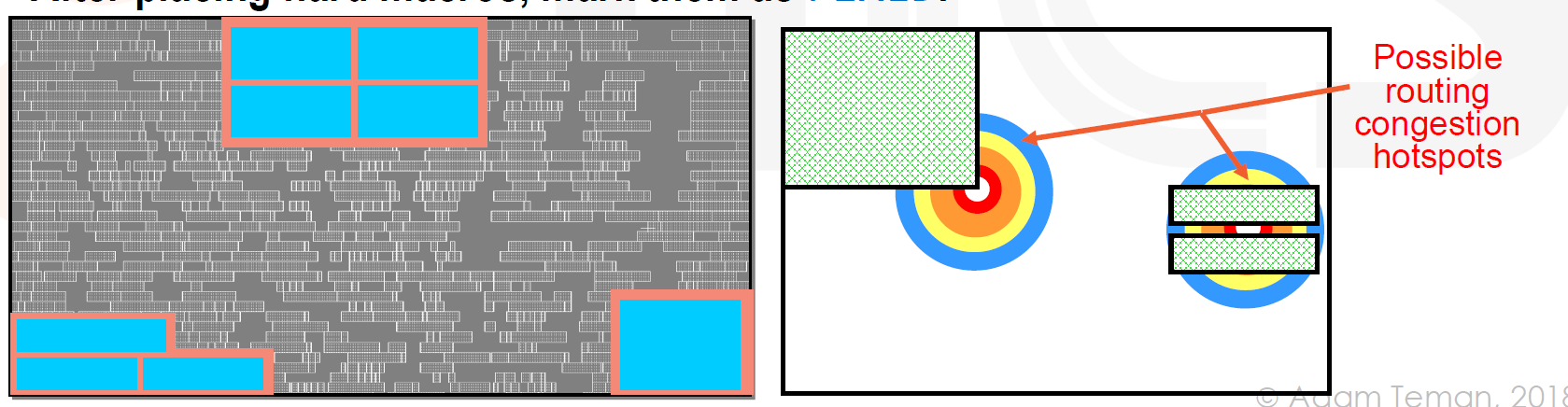

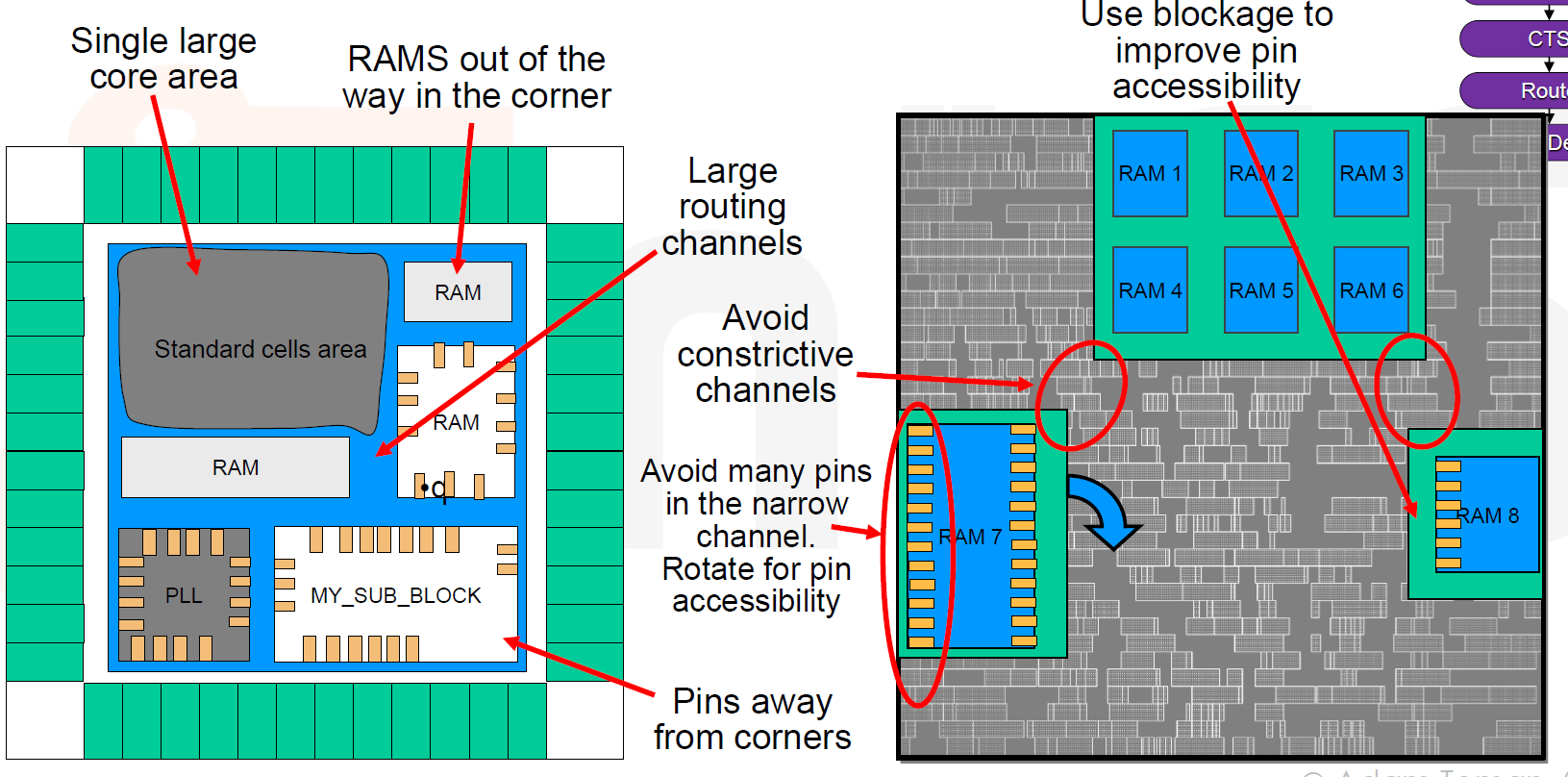

硬宏单元放置(Hard Macro Placement)

- 在放置大型宏单元时,我们必须考虑对布线、时序和功耗的影响。通常将它们推到芯片布局的边缘。

- 放置算法在处理单一大矩形区域时通常表现更好。

- 对于采用线焊封装的芯片,应将高功耗宏单元放在远离芯片中心的位置。

在放置硬宏单元后,应将它们标记为固定(FIXED)。

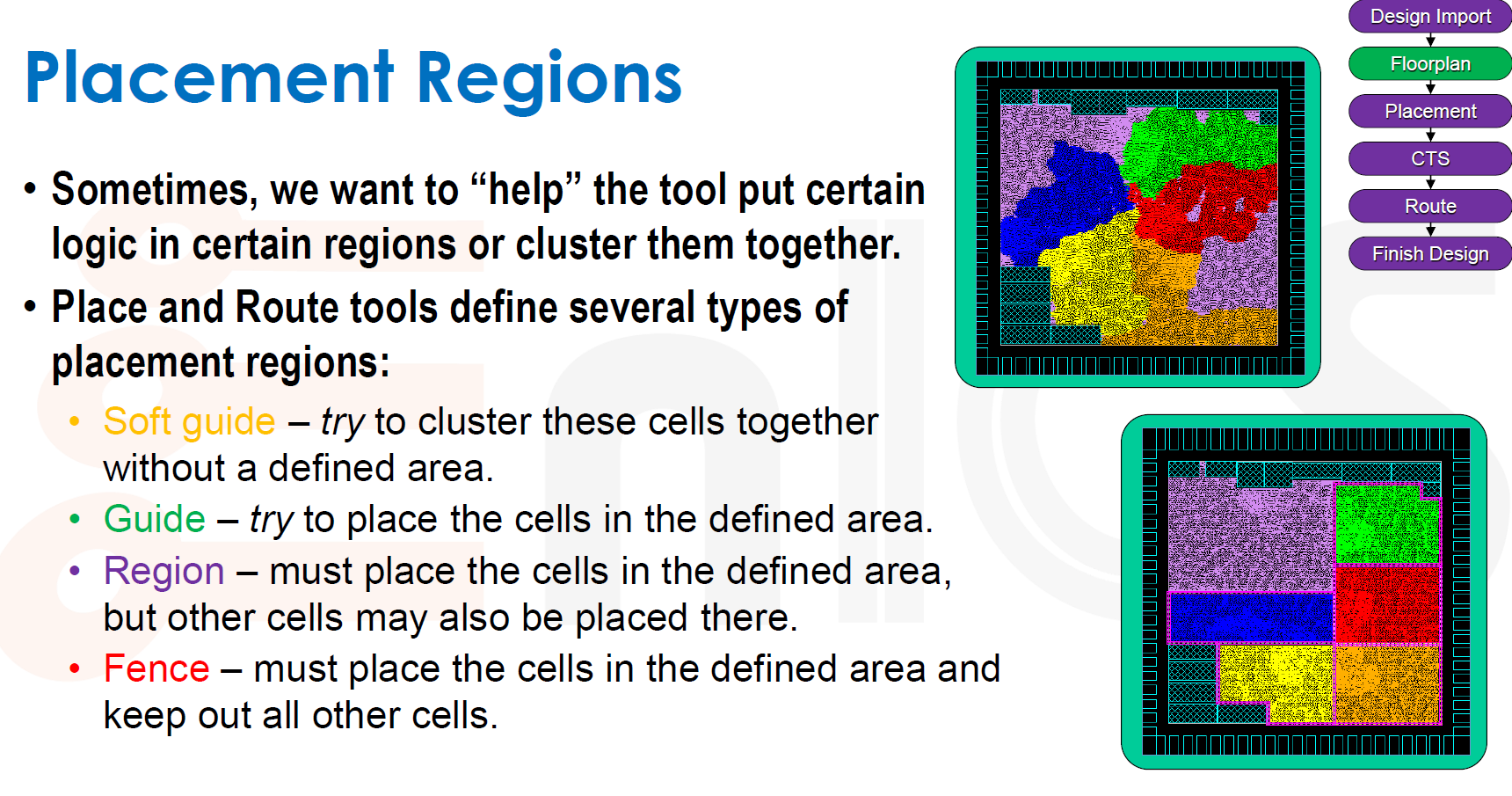

放置区域

有时候,我们希望“辅助工具”将某些逻辑单元放到特定区域,或将它们聚集在一起。

布局与布线工具定义了几种不同类型的放置区域:

图中上面是使用了较弱的约束,下面是使用了较强的约束。

放置阻塞区和光环(Placement Blockages and Halos)

Placement blockage halos 是指工具不能放置任何单元的区域:

- 硬阻塞:完全禁止放置任何单元。

- 软阻塞:放置阶段不可用,但优化阶段可以使用。

- 部分阻塞: 允许放置,但利用率较低。

- 光环区域:是宏单元外围的一圈“缓冲区”,标准单元应避免靠近此区域。

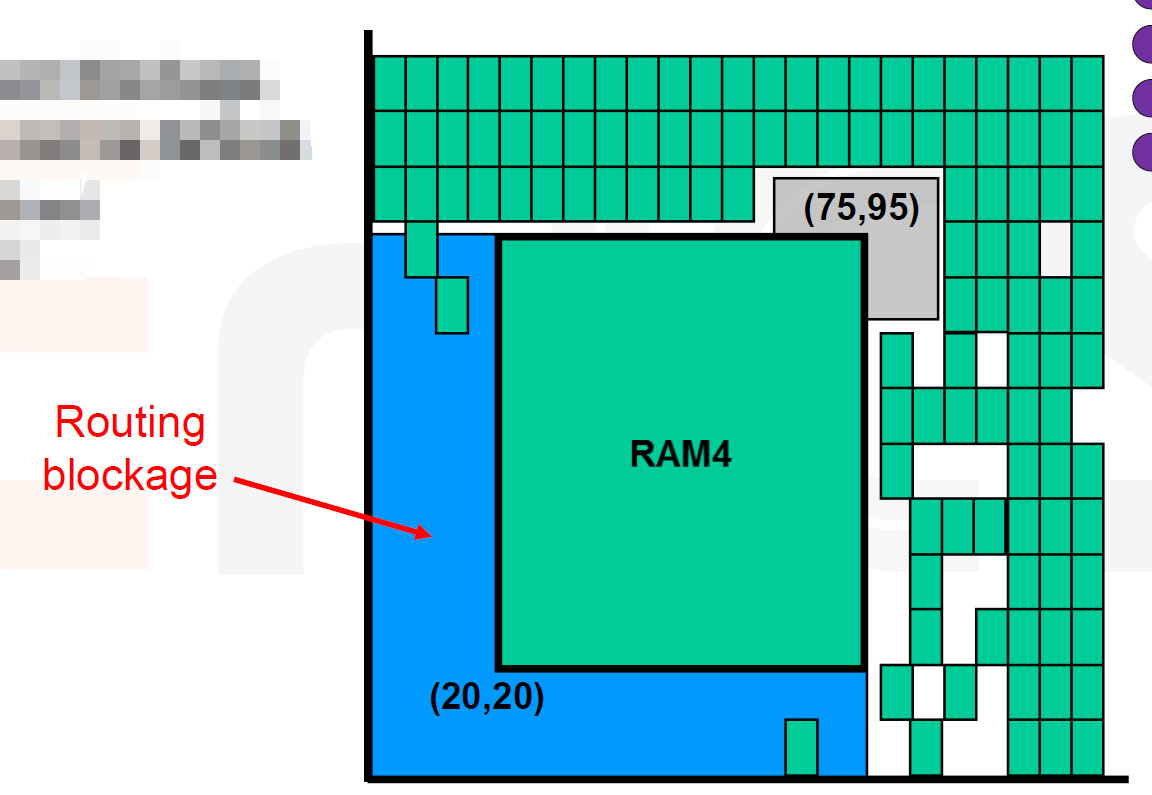

布线阻塞

与放置阻塞类似,也可以定义布线阻塞区域,这是针对特定金属层定义的

良好布局的指导原则

见此图即可。

层次设计

如果设计规模过大,应将其划分为多个层次结构(hierarchies)这样做的优缺点如下:

- 优点

- 运行时间更快,EDA 工具所需内存更少

- ECO(工程更改)响应更迅速

- 支持设计复用

- 缺点

- 整个芯片的时序收敛(timing closure)更困难(ILM)

- 需要更复杂的设计规划,包括通孔路径生成、中继器插入、时序约束分配等等。

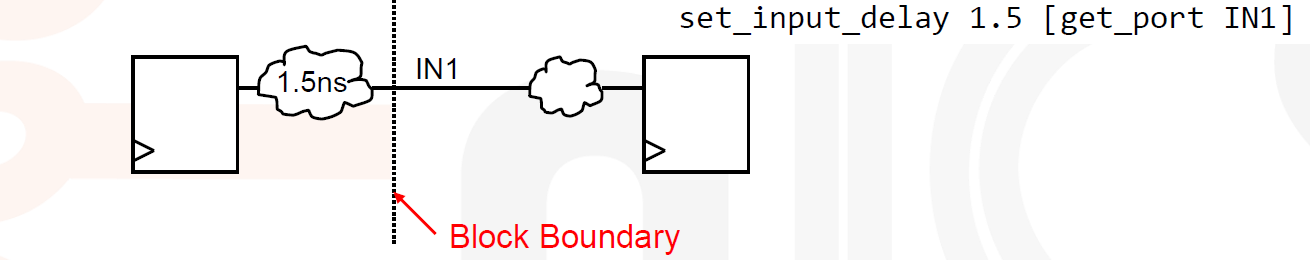

时间预算

芯片级约束必须正确映射为模块级的 I/O 约束,例如当我们设置

set_input_delay 1.5 [get_port IN1]

这表明在模块边界处,IN1的延迟为1.5ns

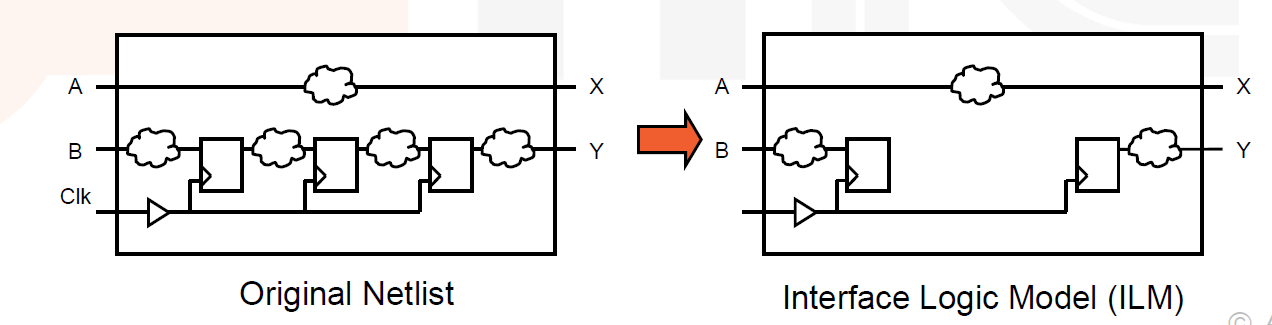

接口逻辑模型(Interface Logic Models ,ILMs)有助于简化并加速过程,它只保留关键的输入输出路径以及时钟路径

引脚分配

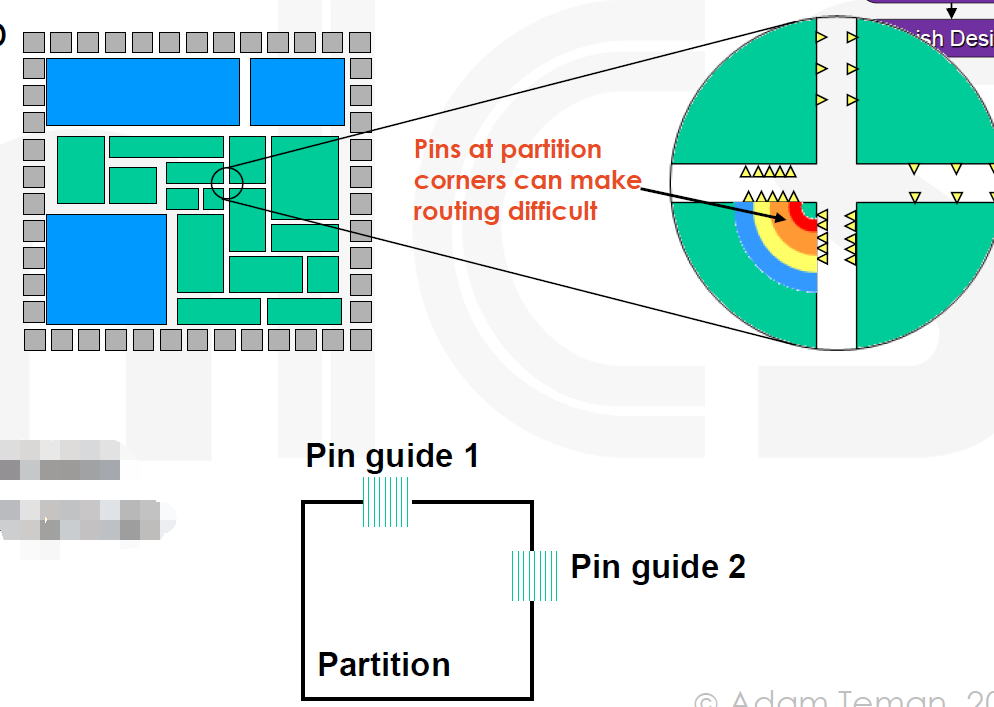

引脚约束包括:层数/间距/尺寸/重叠/网络分组/引脚引导。

引脚可以按照 Placement based (基于连线距离)和 Route based (使用试布线、边界穿越来决定位置)

引脚引导可用于引导特定网络组(net groups)的自动引脚放置,如图所示,这两个引脚引导区域知道网络连接落点。

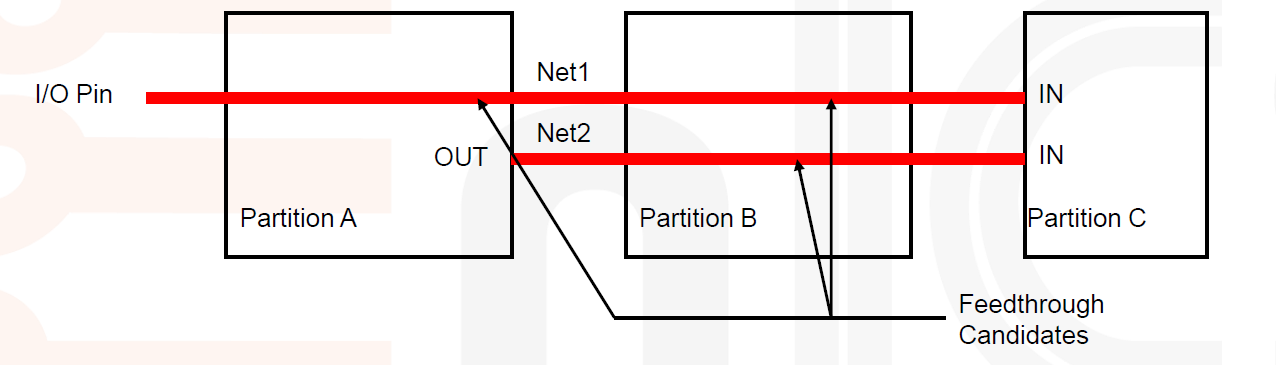

贯通通路

例如我们想要逃实现一个信号从 IO 引脚产生,并且传递到 C 模块,并且需要穿过 A B 两个模块(B 模块不需要处理这个信号)

虽然 B 模块没有处理这个信号,但是你必须考虑成它从哪里进,哪里出,此时设计的复杂度就增加了许多。

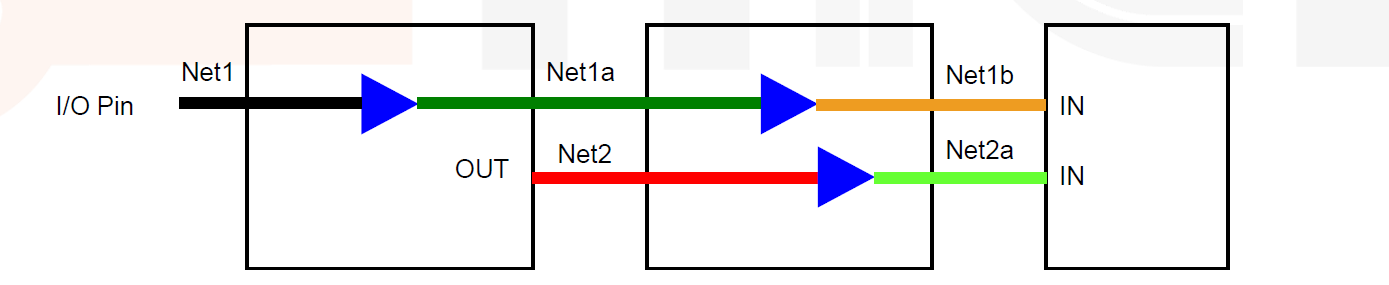

为了支持 feedthrough ,我们可以将原始信号切成多个字段,在每段之间插入缓冲器,每一段都视为新的网络连接,并且可以处理时序、延迟、布线。

设计的效果如图:

- 它有以下优势:

- 可以精细控制信号在每段的传播

- 更容易满足时序约束

- 使层次化设计中的模块之间解耦,便于模块独立综合、布局、验证

功耗规划

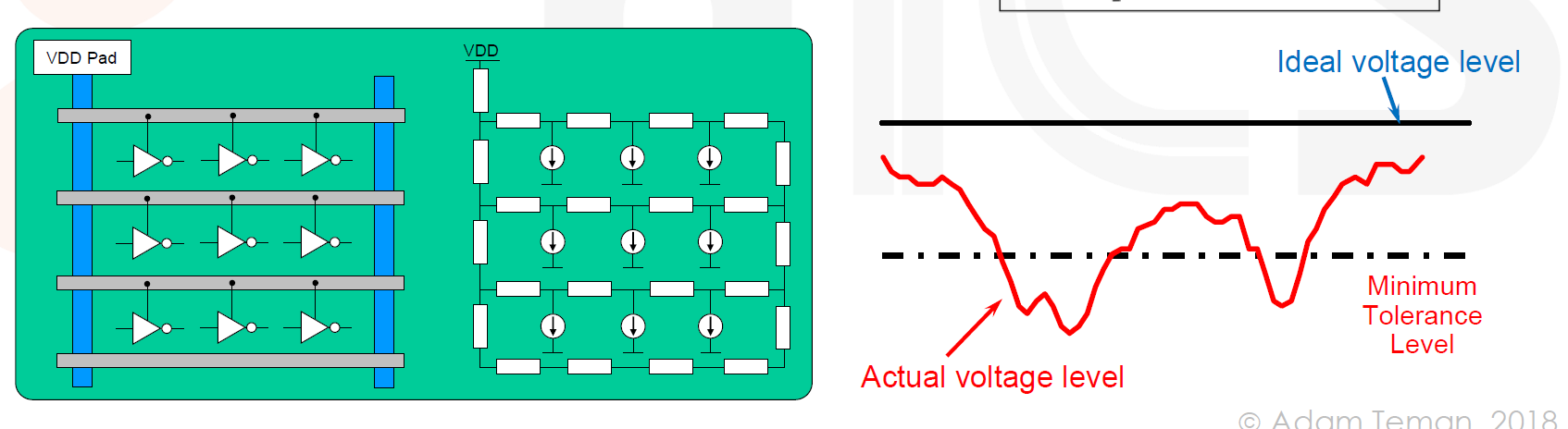

电压下降(IR Drop)

由于电流通过金属线电阻产生压降,导致供电电压降低,为了分析具体下降范围,我们用以下方法分析:

- 构建电源网格的电阻矩阵(resistance matrix)

- 考虑每个逻辑门的平均电流(average current)

- 求解该矩阵,得到每个节点的电流和电压,从而确定 IR Drop

电迁移

由于电流流过导体,导体中的金属原子发生逐渐位移的现象,这本质是电子动量的传递,它会导致开路、短路或者吸能下降(导致导线RC值发生变化)。

Power Distribution

-

电源分布网络有如下优点:

- 从电源焊盘向芯片上的晶体管输送电流(current)

- 保持电压稳定且低噪声

- 提供平均与峰值的功率需求

- 为信号提供电流回路

- 避免电迁移与自热导致的损耗

- 尽量少占用芯片的面积与金属线

- 便于布局设计

-

使用更宽的电源线优点

- 降低IR Drop

- 降低动态压降

- 降低电迁移风险

- 但是,使用更宽的电源线会导致布线资源减少。

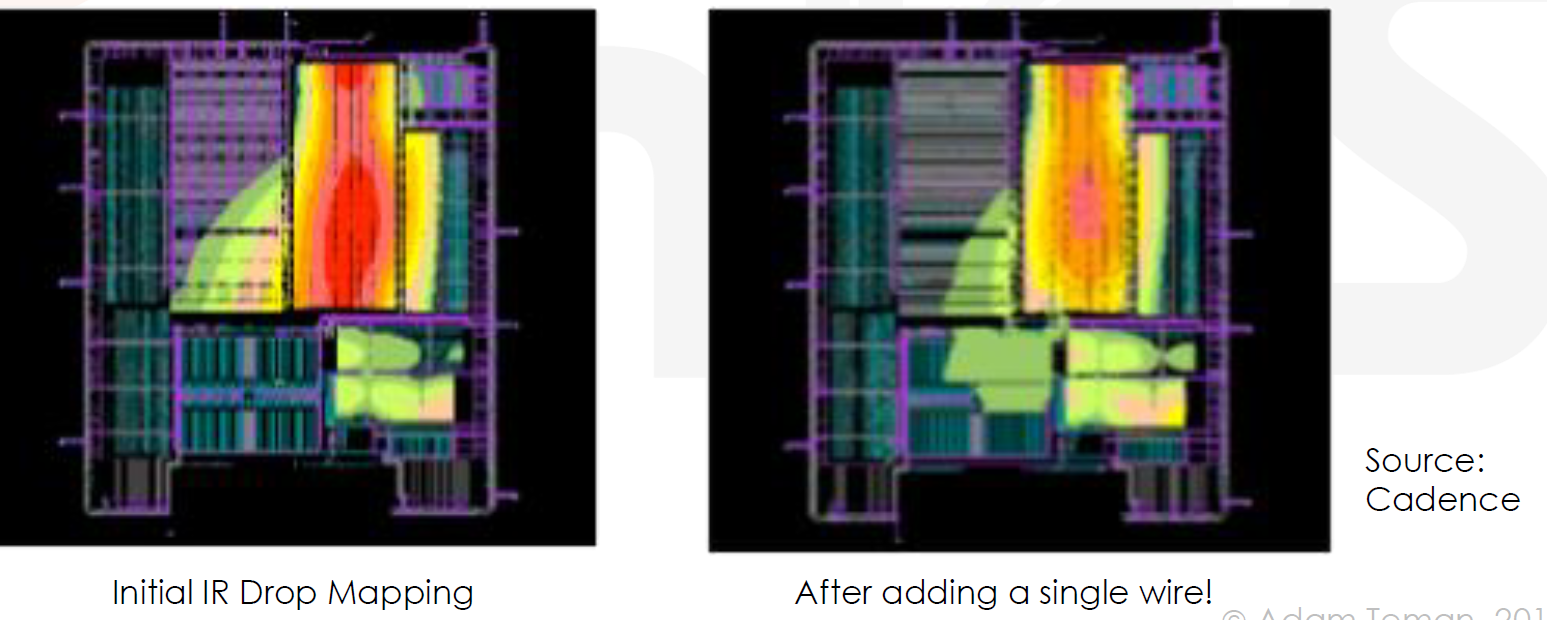

Hot Spots

通常用 color map 对芯片的IR Drop进行可视化映射

电源与地线布线

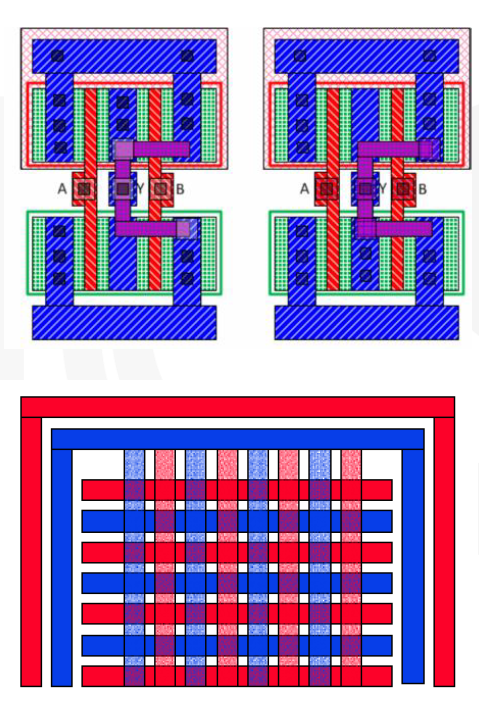

每个标准单元或者宏单元都包含 VDD(电源)和 GND(地线)信号,他们必须被链接起来。

- 使用电源/地线网络,允许电源/地从源端传输到目标的多条路径,能够带来以下好处:

- 更低的串联电阻

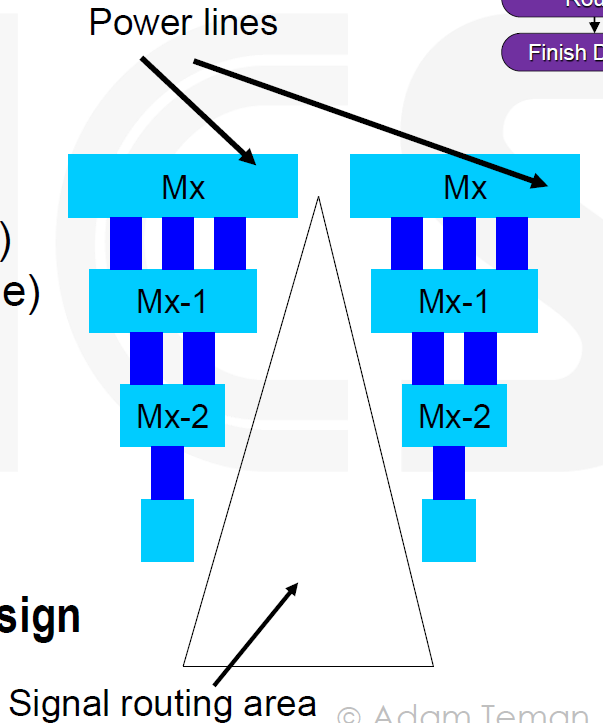

- 使用分层式电源与地线网格,从高层金属布线延伸至低层

- 各层之间通过 vias 进行连接

这是个非常庞大的网络,他们通常是规则的,并且 、P/G 布线资源一般是预留好的。

标准电源布线方法

目前最常见的是电源网格,它使用相互连接的垂直和水平电源条,在上层金属层中,VDD/GND 通常占用了一半以上的资源

其次还有专用 VDD/GND 平面,这种成本非常高,但是可以进行电路分析

- 同时,有一些趋势和想法:

- 电源/地线与 I/O 焊盘协同优化,配合传统物理设计

- 使用去耦电容,降低因电源网络引起的电压下降

- 使用多电压/多频率岛,会使电源/地线问题与时钟分布变得更具挑战性

创建电源网格

你需要在IR Drop 和 EM(电迁移)中进行权衡,你会评估功耗和平均电流与最大电流密度。

- 还需要确定以下下内容

- 总体网格结构(例如:是否使用门控、是否多电压)

- 每种电压对应的电源焊盘数量与位置

- 选用的金属层

- 电源条的宽度与间距

- 通孔堆叠 和 可用布线资源

- 是否使用电源环

- 分层模块的屏蔽设计

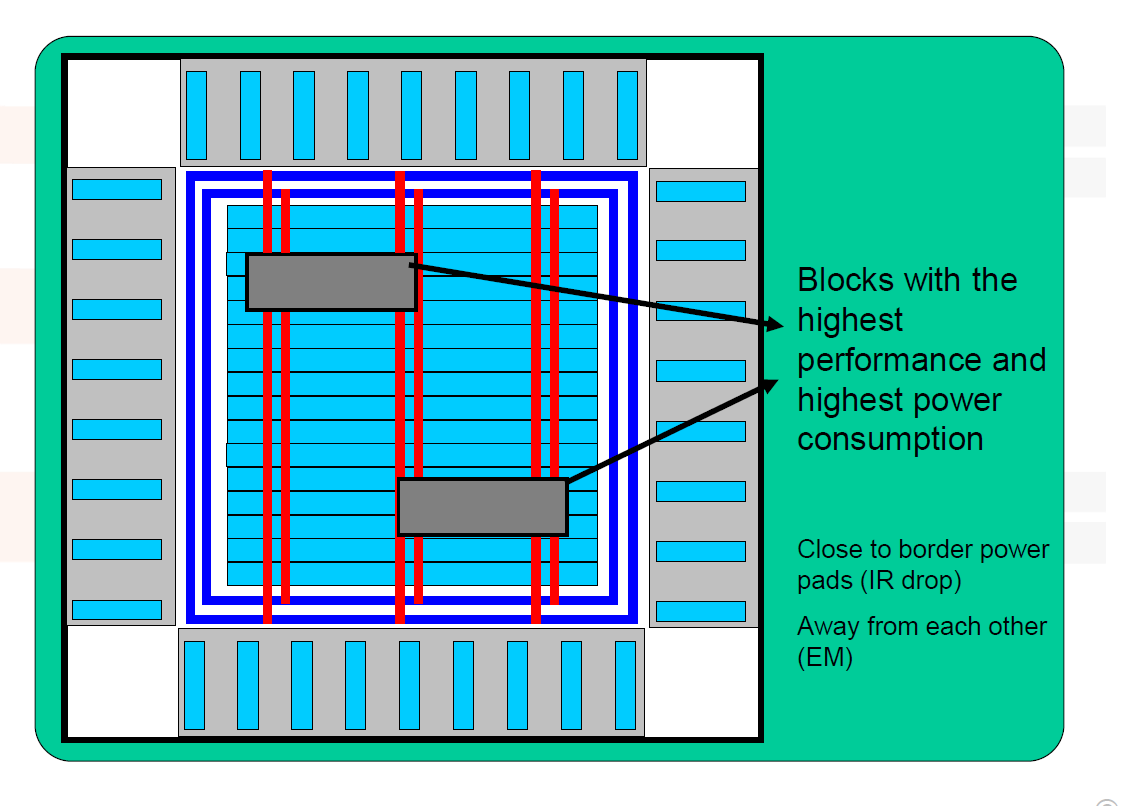

宏单元布局

功耗较高、性能最强的模块需要尽可能靠近边缘的电源焊盘(避免 IR Drop),并且必须保持距离避免 EM

总结

进行 Floorplanning 之前,你已经完成了以下内容: